### MONOLITHIC INDUCTORS

# FOR SILICON RADIO FREQUENCY INTEGRATED CIRCUITS

by

Mina Danesh

A thesis submitted in conformity with the requirements for the degree of Master of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto

© Copyright by Mina Danesh 1999

#### National Library of Canada

#### Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-45607-2

## Monolithic Inductors for Silicon Radio Frequency Integrated Circuits

Mina Danesh

Master of Applied Science Department of Electrical and Computer Engineering University of Toronto 1999

### ABSTRACT

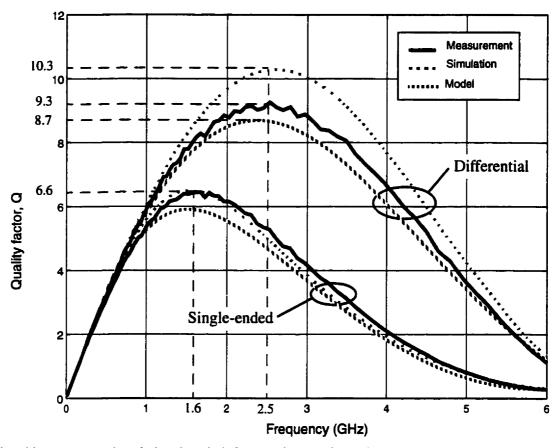

A novel parameter extraction technique is applied to the modeling of rectangular spiral inductors and validated with measurements and simulations. To enhance the inductor quality (Q) factor, a differentially excited symmetric inductor is used. Compared with a single-ended configuration, the differential structure offers a higher Q-factor over a wider range of frequencies. Application of the symmetric inductor model is demonstrated using two oscillator designs in which a differentially excited symmetric inductor is compared with conventional spiral inductors. The symmetric inductor improves the overall circuit performance and saves chip area.

### ACKNOWLEDGMENTS

I wish to thank Professor John R. Long for introducing me to the world of RF electronics, and in particular, to microstrip structures on semiconductors, where electromagnetics is coupled to electronics. He helped me in many ways throughout the course of my studies. I appreciate his patience and his sympathy.

I am also grateful to my fellow graduate students and friends: Ramesh Abhari (Yes, you will be a professor!), Xidong Wu (for his Eastern philosophy and insightful comments), Leesa and Karam Noujeim, Micah Stickel, Sebastian Magierowski, Dickson Cheung, Ali Sheikholeslami, Vincent Gaudet, and Mr. Gerald Dubois who plays a special role in the group. I also appreciate having met many interesting people, as well as the Massey College community, who made my stay in Toronto much more enjoyable. I shall not forget Behzad, a soulful musician.

Je tiens à remercier mes parents et toute ma famille pour leur appui au cours de ces deux dernières années. Karima a aussi tenu une place que je ne saurai décrire. Nilda et Alexandra demeureront mes amies pour toujours.

I am thankful for the NSERC Graduate Scholarship which gave me the opportunity to come to the University of Toronto.

Finally, I wish to thank Prof. Christopher W. Trueman who knows how to guide his students in their research.

"One is capable, if one is knowledgeable Knowledge (danesh) rejuvenates the soul" Ferdowsi (940 - 1020 A.D.)

iii

### FOREWORD

This thesis is mainly aimed at RF circuit engineers. For those who do not have any previous knowledge of how a spiral inductor works, the mechanisms behind microstrip structures on a silicon substrate are presented. Chapter 2 explains the fundamentals of a single microstrip line. Even though the world of electromagnetics may seem to exist in a realm other than microelectronics, this is in fact not the case. One must realize that electromagnetics (EM) is the basis of everything electrical. I have tried to explain the interactions of the EM fields in semiconductors as simply as possible. I deliberately did not give any formulations regarding EM fields for they might confuse the reader. Since circuit engineers love circuits, equivalent circuit models for monolthic inductors are given, which should simplify their application in a circuit simulator.

For those who already have some experience with spiral inductors, Chapters 3 and 4 present new approaches to the modeling and optimization techniques for inductors. Differential circuits may seem very familiar, but the designer rarely considers the EM mechanism behind a differentially excited microstrip line or a different inductor configuration. Chapter 4 gives an example of a cross-coupled oscillator where two inductor configurations are compared.

A bibliography is given for those interested in further investigation. It is not an extensive list, but it covers the major references.

Mina Danesh September 1998

## **TABLE OF CONTENTS**

page

| LIST OF FIGURES                                                          | vii |

|--------------------------------------------------------------------------|-----|

| LIST OF TABLES                                                           | x   |

| LIST OF SYMBOLS                                                          | xi  |

| 1. INTRODUCTION                                                          | 1   |

| 1.1 Silicon Radio Frequency Integrated Circuits                          | 1   |

| 1.2 Microwave Monolithic Inductors                                       | 3   |

| 1.3 Purpose and Organization of this Thesis                              | 5   |

| 2. SILICON MICROSTRIP STRUCTURE CHARACTERISTICS                          | 7   |

| 2.1 Wave Propagation Modes                                               | 7   |

| 2.2 Lumped Circuit Modeling                                              | 14  |

| 2.2.1 Single Microstrip Line Modeling                                    | 14  |

| 2.2.2 Spiral Inductor Modeling                                           |     |

| 2.3 Inductor Quality Factor                                              |     |

| 2.4 Parameter Extraction Methods                                         | 19  |

| 2.4.1 Parameter Extraction from Two-Port Results                         |     |

| 2.4.2 Analytical Parameter Extraction                                    |     |

| a) Inductance                                                            |     |

| b) Capacitance                                                           |     |

| c) Resistance                                                            |     |

| d) Temperature Dependence                                                |     |

| 2.5 Microstrip Line Simulation and Modeling<br>2.5.1 Approximation Model |     |

| 2.5.2 Results                                                            |     |

| 3. SPIRAL INDUCTOR MODELING                                              |     |

| 3.1 Motivation                                                           |     |

| 3.2 Modeling Procedure                                                   |     |

| -                                                                        |     |

| 3.2.1 Inductance                                                         |     |

| 3.2.3 Substrate Parasitics                                               |     |

| a) Substrate Capacitance                                                 |     |

| b) Substrate Resistance                                                  |     |

| 3.2.4 Line-to-line Capacitance                                           |     |

| 3.2.5 Final Inductor Model                                               |     |

| 3.3 Test Structures                                                      | 41  |

| 3.4 Results and Discussion                                               | 41  |

| 4. SYMMETRIC INDUCTORS FOR DIFFERENTIAL CIRCUITS | 46 |

|--------------------------------------------------|----|

| 4.1 Motivation                                   | 46 |

| 4.2 Review of <i>Q</i> Enhancement Techniques    |    |

| 4.2.1 Optimization by Inductor Design            |    |

| 4.2.2 Optimization by Reducing Ohmic Losses      |    |

| 4.2.3 Optimization by Reducing Substrate Losses  |    |

| 4.3 Review of Inductor Chip Area Reduction       |    |

| 4.4 Proposed Method                              |    |

| 4.4.1 Inductors for Differential Circuits        |    |

| 4.4.2. Asymmetrical vs. Symmetrical Inductors    |    |

| 4.5 One-Port Excitation Theoretical Analysis     |    |

| 4.6 Test Structure                               |    |

| 4.7 Symmetric Inductor Modeling                  |    |

| 4.8 Measurement Procedure                        |    |

| 4.8.1 Calibration                                |    |

| 4.8.2 De-embedding Procedure                     |    |

| 4.8.3 Single-ended vs. Differential Parameters   |    |

| 4.9 Results                                      |    |

| 4.9.1 Parasitics                                 | 63 |

| 4.9.2 Results and Discussion                     | 63 |

| 4.9.3 Sources of Error                           | 68 |

| 4.9.4 Optimized Equivalent Circuit Models        | 68 |

| 4.9.5 Comparisons with the Literature            | 69 |

| 4.10 Application                                 |    |

| 4.10.1 Oscillator Design                         | 70 |

| 4.10.2 Colpitts Oscillator                       | 71 |

| a) Operating Points                              | 72 |

| b) Results                                       |    |

| 4.10.3 Cross-coupled Oscillator                  |    |

| a) Operating Points                              |    |

| b) Results                                       | 75 |

| 5. CONCLUSIONS                                   |    |

| REFERENCES                                       | 81 |

## LIST OF FIGURES

| page                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. RF front-end: heterodyne transceiver architecture                                                                                                                                                                                                                                                             |

| 2. Silicon resistivity as a function of doping concentrations of n-type (phosphorus) and p-type (boron)                                                                                                                                                                                                          |

| 3. Microstrip line on silicon with a typical range of parameter values                                                                                                                                                                                                                                           |

| <ul> <li>4. Monolithic inductor configurations: (a) Microstrip line, (b) Meander line, (c) Single loop,</li> <li>(d) Circular spiral, (e) Octogonal spiral, (f) Rectangular spiral</li></ul>                                                                                                                     |

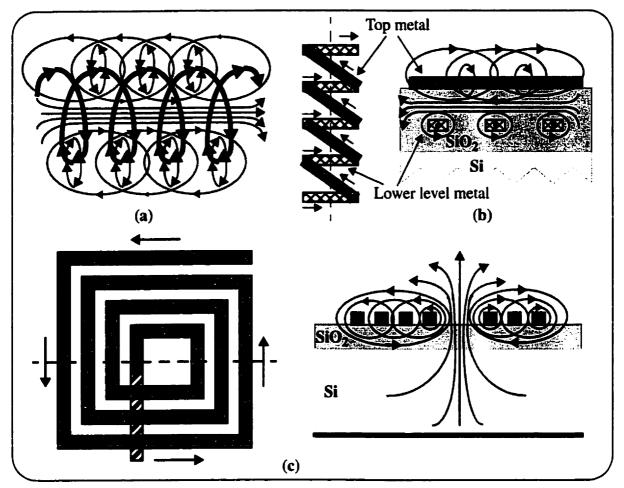

| 5. Magnetic field lines for (a) an air coil, (b) a planar solenoid, and (c) a planar rectangular spiral inductor                                                                                                                                                                                                 |

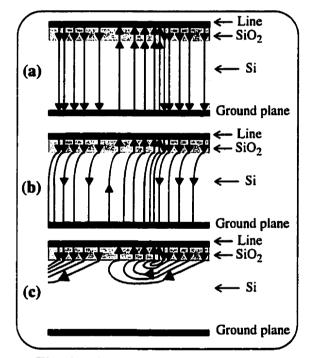

| 6. Electric field distribution of (a) quasi-TEM, (b) slow-wave, and (c) skin-effect modes                                                                                                                                                                                                                        |

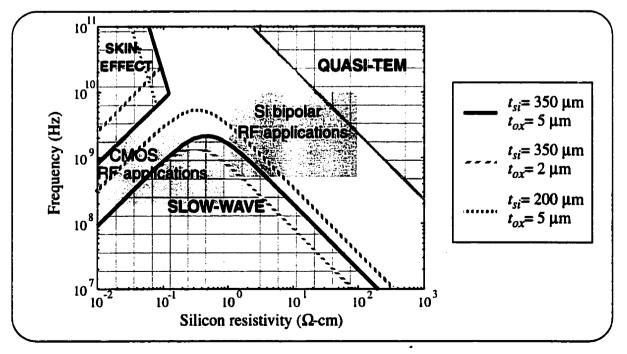

| 7. Resistivity-frequency mode chart for various oxide/silicon thicknesses                                                                                                                                                                                                                                        |

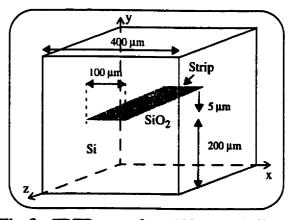

| 8. FDTD space for a 100 µm strip line9                                                                                                                                                                                                                                                                           |

| 9. Unnormalized vertical electric field for $\rho_{si} = 0.1 \Omega$ -cm                                                                                                                                                                                                                                         |

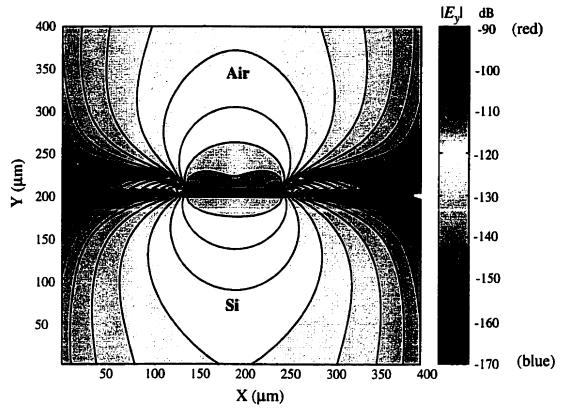

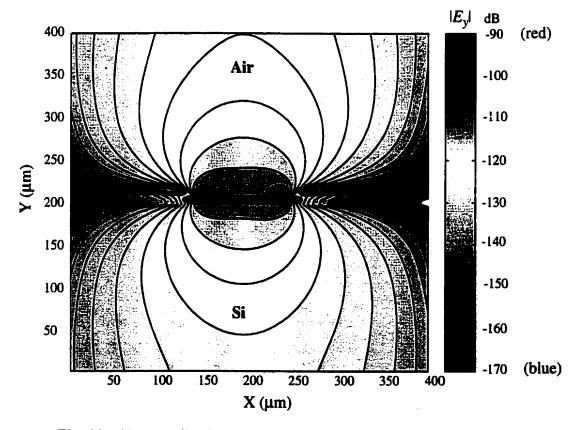

| 10. Unnormalized vertical electric field for $\rho_{si} = 10 \Omega$ -cm                                                                                                                                                                                                                                         |

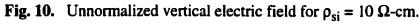

| 11. Unnormalized vertical electric field for $\rho_{si} = 10 \text{ k}\Omega$ -cm                                                                                                                                                                                                                                |

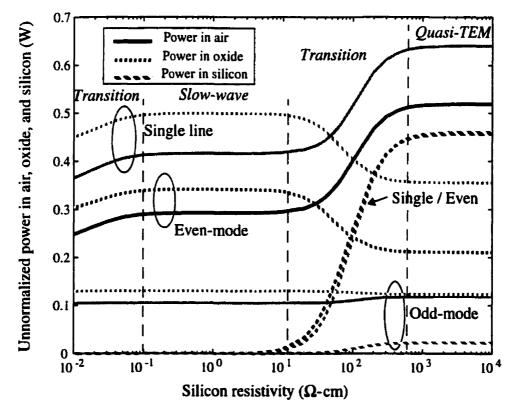

| 12. Unnormalized power in air, oxide and silicon for a single line, and even-mode and odd-<br>mode excitations of two coupled microstrip lines ( $w = 10 \ \mu m$ , $s = 5 \ \mu m$ ) at 1 GHz11                                                                                                                 |

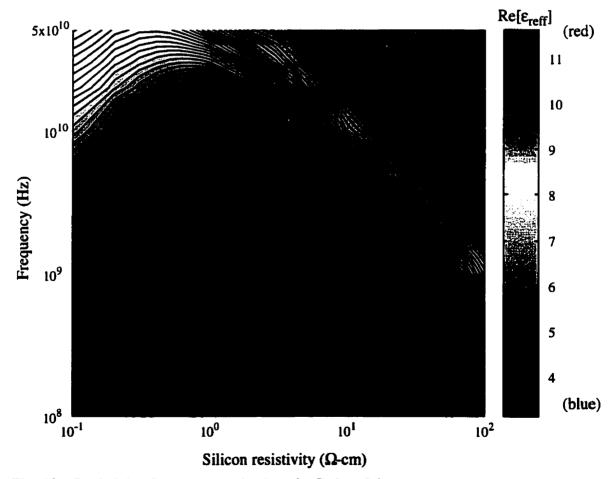

| 13. Resistivity-frequency mode chart for Re[ $\varepsilon_{reff}$ ] for a 10 µm wide microstrip line                                                                                                                                                                                                             |

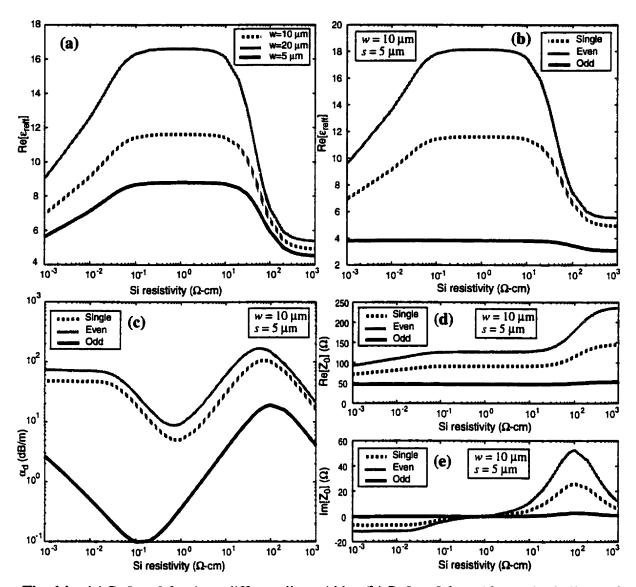

| <ul> <li>14. (a) Re[ε<sub>reff</sub>] for different line widths. (b) Re[ε<sub>reff</sub>] for a 10 µm single line and coupled lines with 5 µm spacing. (c) Attenuation for single and coupled lines. (d) Real part and (e) imaginary part of the characteristic impedance for single and coupled lines</li></ul> |

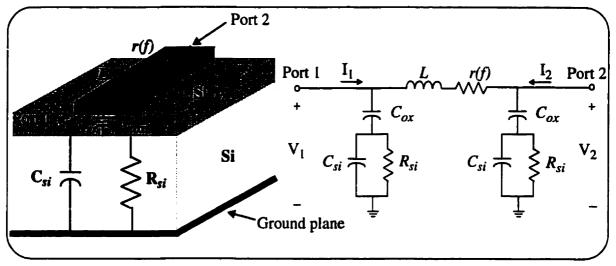

| 15. Microstrip line equivalent circuit                                                                                                                                                                                                                                                                           |

| 16. Surface current flow for spiral inductors of (a) 3.75 turns and (b) 6.5 turns at 1 GHz15                                                                                                                                                                                                                     |

| 17. Electromagnetic field lines and line parameters for two coupled lines for odd- and even-<br>mode excitations                                                                                                                                                                                                 |

| 18. Simplified spiral inductor layout17                                                                                                                                                                                                                                                                          |

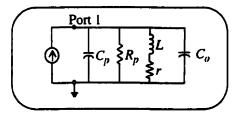

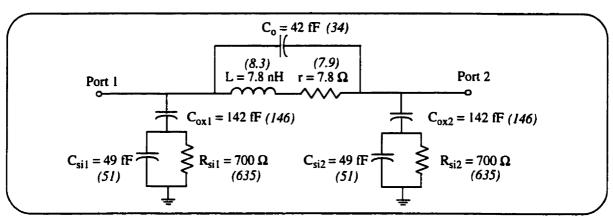

| 19. Compact lumped element inductor model17                                                                                                                                                                                                                                                                      |

| 20. Equivalent 1-port model                                                                                                                                                                                                                                                                                      |

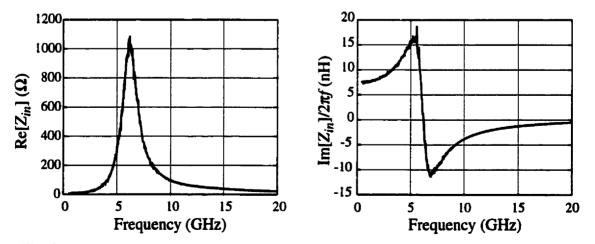

| 21.         | Measured real and imaginary parts of input impedance of a symmetric spiral indutor (N=5, $w=8 \mu m$ , $s=2.8 \mu m$ )                                                          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22.         | Parameter fit circuit model for measured and (simulated) CMOS spiral inductor20                                                                                                 |

| 23.         | Parameter extraction by the transmission matrix                                                                                                                                 |

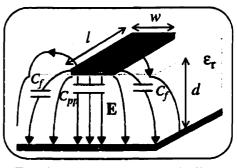

| 24.         | MMIC microstrip line with shown electric fields22                                                                                                                               |

| 25.         | Odd-mode capacitances for two coupled microstrip lines                                                                                                                          |

| 26.         | Current distribution for an MMIC microstrip line24                                                                                                                              |

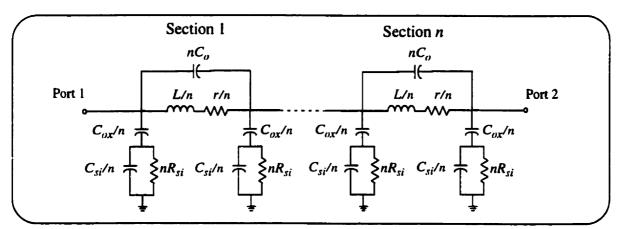

| 27.         | Distributed model of a microstrip line with two sections                                                                                                                        |

| 28.         | Inductance L and series resistance r for 1 mm long microstrip lines                                                                                                             |

| 29.         | Equivalent shunt substrate parasitics                                                                                                                                           |

| 30.         | Substrate capacitance and resistance for 1 mm long microstrip lines                                                                                                             |

| 31.         | Quality factor for 1 mm long microstrip lines                                                                                                                                   |

| 32.         | Lumped element circuit model for one and a half turns of a spiral inductor                                                                                                      |

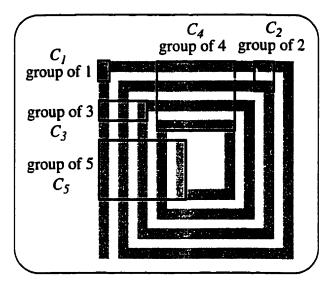

| 33.         | A 4.25 turn spiral inductor with different groups of coupled lines for line capacitances37                                                                                      |

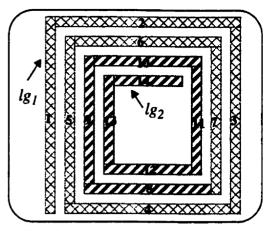

| 34.         | A 3.5 turn spiral inductor divided into two lengths                                                                                                                             |

| 35.         | Representation of the interwinding and underpass capacitances                                                                                                                   |

| 36.         | Distributed model for the spiral inductor equivalent circuit40                                                                                                                  |

| 37.         | Photomicrograph of a 4.25 turn, 5 nH spiral inductor of 15 $\mu$ m width and 1 $\mu$ m spacing.41                                                                               |

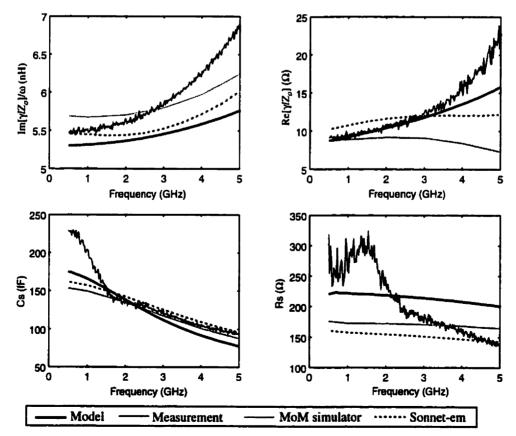

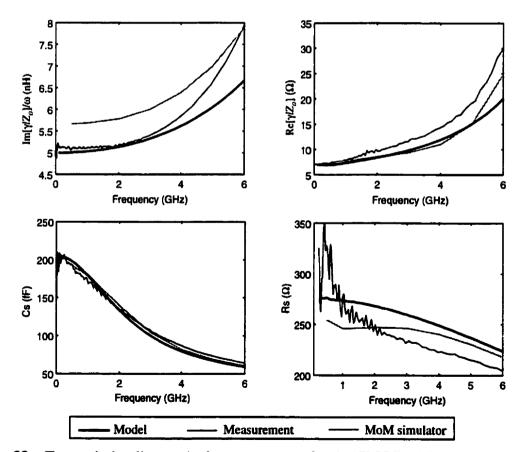

| 38.         | Transmission line equivalent parameters for the BiCMOS 4.5 turn inductor42                                                                                                      |

| <b>39</b> . | Transmission line equivalent parameters for the CMOS 4.25 turn inductor43                                                                                                       |

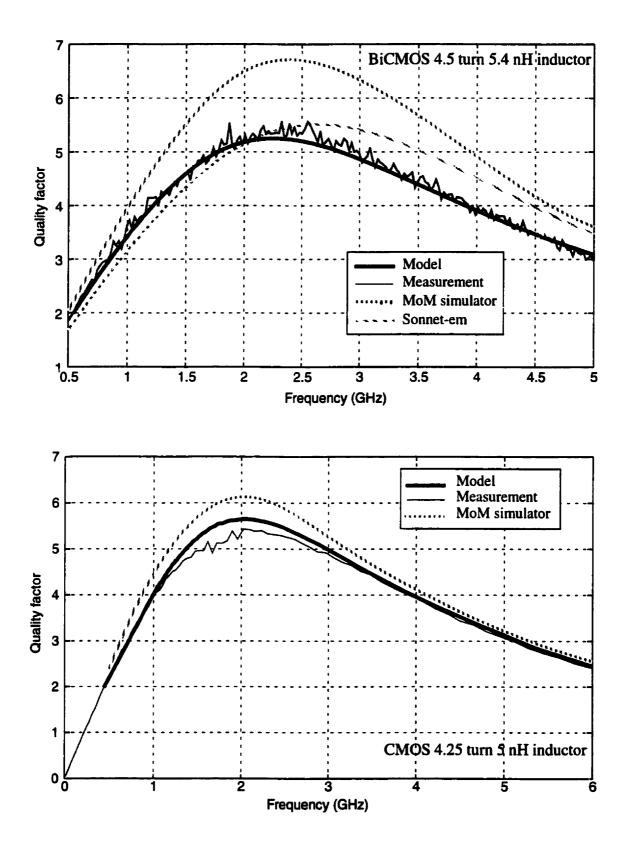

| 40.         | <i>Q</i> -factor comparisons between models, measurements, and simulations for two spiral inductors                                                                             |

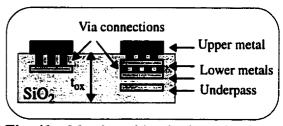

| 41.         | Metal stacking in the oxide layer48                                                                                                                                             |

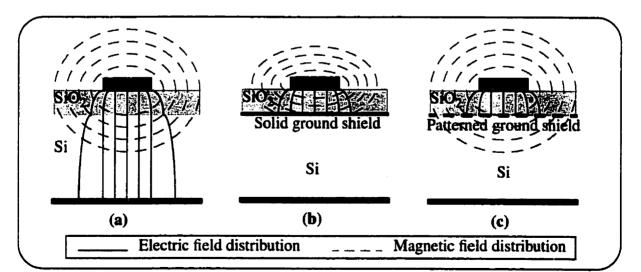

| 42.         | Electric and magnetic field distributions for microstrip lines (a) without a ground shield, (b) with a ground shield, and (c) with a patterned ground shield                    |

| 43.         | Patterned ground shield                                                                                                                                                         |

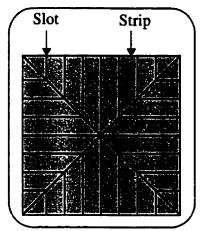

| 44.         | Removal of substrate parasitics by (a) selective etching of the underlying silicon, (b) fabrication of a dielectric membrane, or (c) etching part of oxide and silicon layers50 |

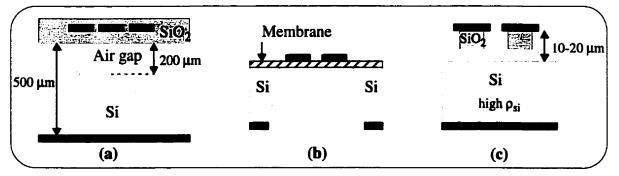

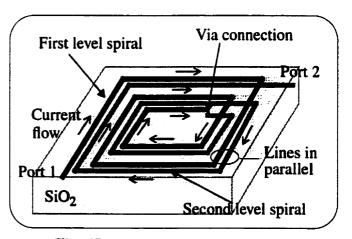

| 45.         | Multilevel spiral inductor                                                                                                                                                      |

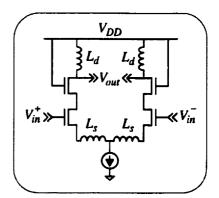

| 46.         | Differential LNA53                                                                                                                                                              |

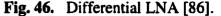

|              | Differential excitation for (a) two adjacent asymmetrical spiral inductors and a (b) Single ymmetrical inductor                     |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

| <b>48.</b> C | Current paths for (a) single-ended and (b) differential connections                                                                 |

| <b>49.</b> S | Single-ended excitation model55                                                                                                     |

| <b>50.</b> C | Differential excitation model55                                                                                                     |

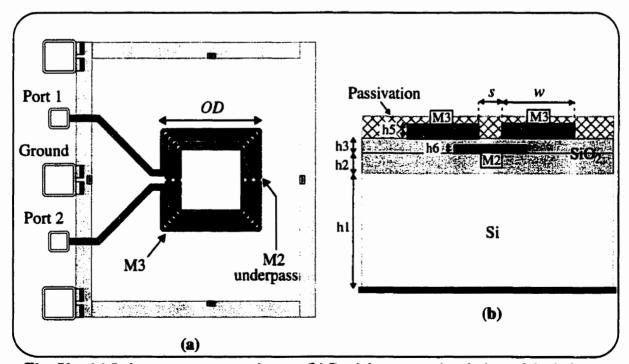

|              | a) Inductor test structure layout. (b) Partial cross-sectional view of the nductor                                                  |

| <b>52.</b> C | Open and short dummies for the inductor in Fig. 51 (a)57                                                                            |

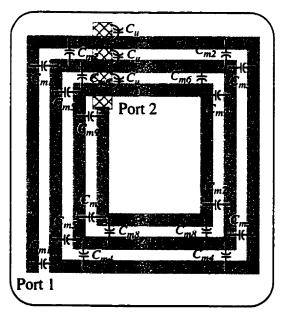

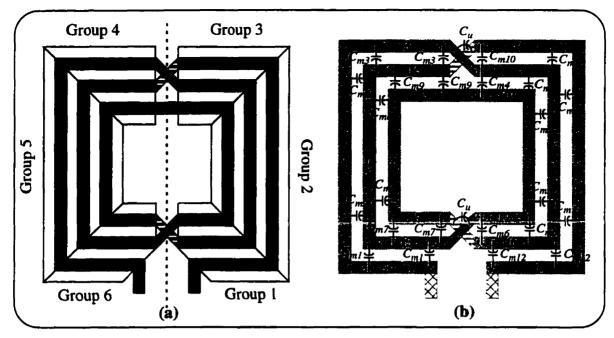

|              | turn symmetric inductor modeling with (a) group sectioning and (b) line-to-line<br>apacitances                                      |

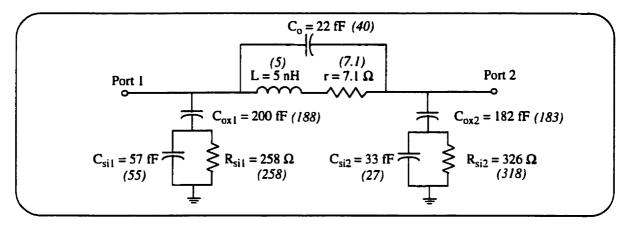

| <b>54.</b> P | Parameter fit circuit model for measured and (simulated) symmetric inductor59                                                       |

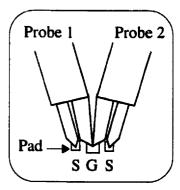

| <b>55.</b> E | Dual probes                                                                                                                         |

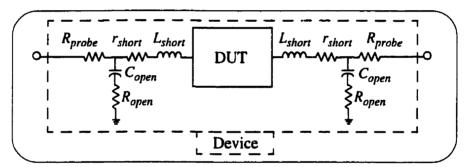

| <b>56.</b> E | Device under test with associated parasitics60                                                                                      |

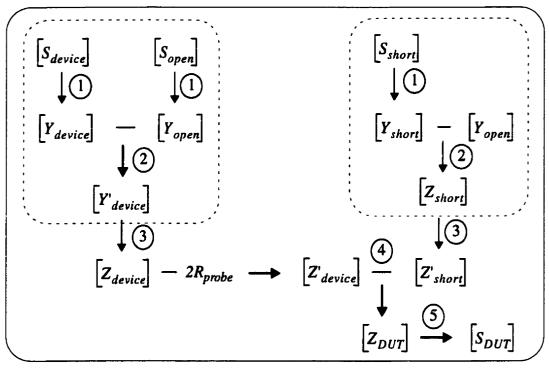

| <b>57.</b> F | Flowchart of de-embedding steps61                                                                                                   |

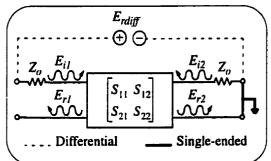

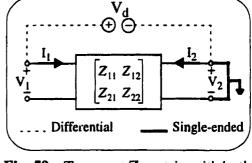

| <b>58.</b> T | Two-port S-matrix with both configurations61                                                                                        |

| <b>59.</b> T | Two-port Z-matrix with both configurations62                                                                                        |

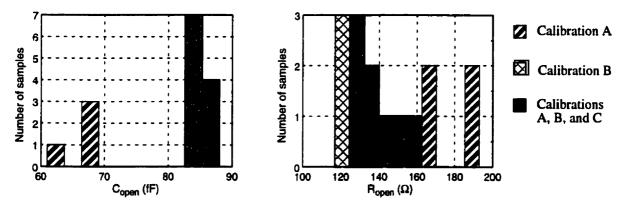

| <b>60.</b> C | Open dummy structure parasitic histograms over 15 samples63                                                                         |

| <b>61.</b> I | nductor structure histograms over 19 samples for (a) L and r at 500 MHz and (b) Q64                                                 |

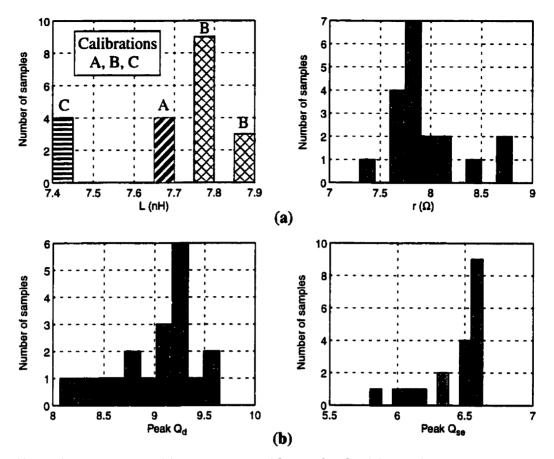

| <b>62.</b> T | Fransmission line equivalent parameters for the 8 nH symmetric inductor65                                                           |

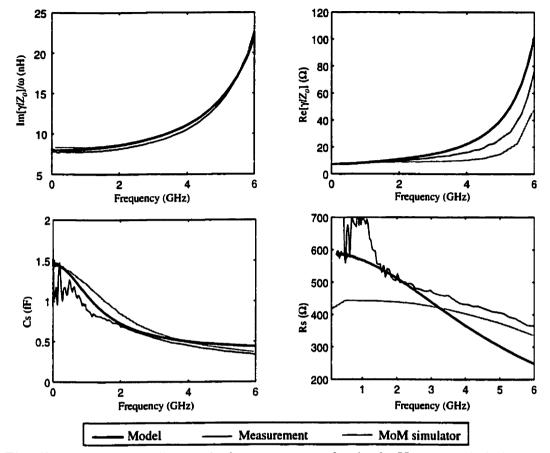

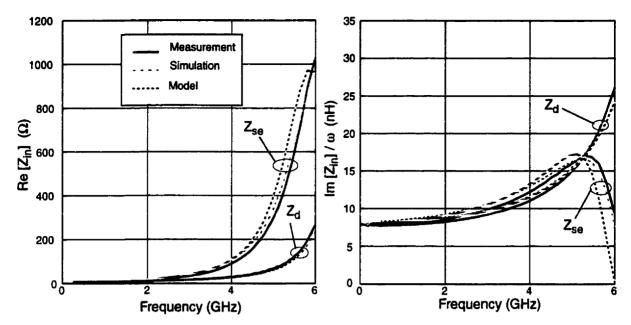

|              | Measured and simulated resistive and inductive parts of input impedances for single-ended<br>and differential connections           |

| <b>64.</b> N | Measured and simulated Q-factors for single-ended and differential excitations67                                                    |

| <b>65.</b> ( | Optimized equivalent circuit model for both configurations                                                                          |

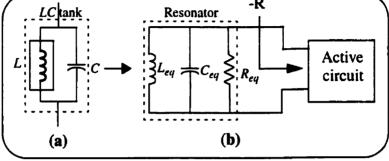

| <b>66.</b> ( | <b>a</b> ) <i>LC</i> tank and ( <b>b</b> ) equivalent resonator in a one-port oscillator71                                          |

| 67. (        | Colpitts oscillator circuit                                                                                                         |

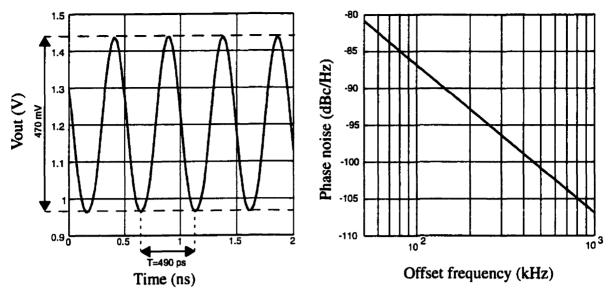

| <b>68.</b> ( | Output oscillating voltage and phase noise for the Colpitts shown in Fig. 67                                                        |

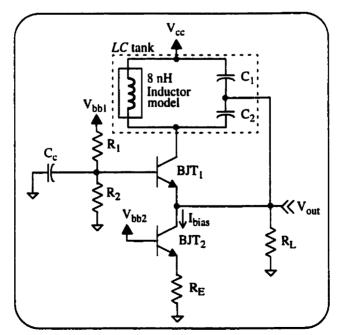

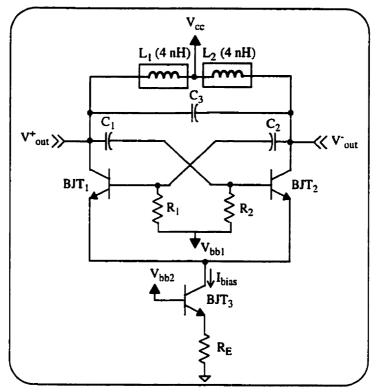

| <b>69.</b> ( | Cross-coupled oscillator circuit74                                                                                                  |

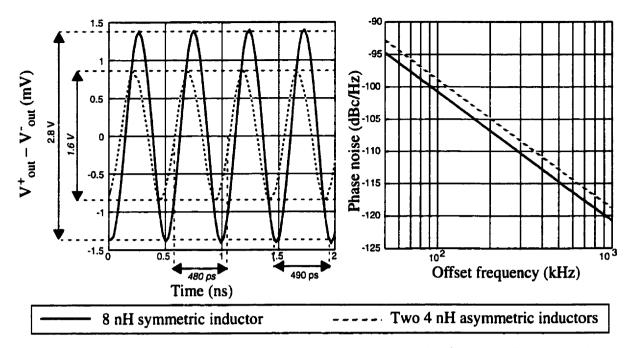

|              | Differential output voltage oscillation and phase noise for the 8 nH symmetric inductor<br>and two 4 nH asymmetric spiral inductors |

## LIST OF TABLES

|                                                                                    | page |

|------------------------------------------------------------------------------------|------|

| <b>1.</b> Microstrip line inductance comparison for $\rho_{si} = 10 \Omega$ -cm    | 29   |

| 2. Lumped element values for spiral inductor models                                | 42   |

| 3. Typical inductor Q-factors for standard Si IC processes                         | 46   |

| 4. Comparisons with series and parallel connected inductors                        | 52   |

| 5. Substrate and metal parameters                                                  | 57   |

| 6. Lumped element values for the 5 turn symmetric inductor                         | 59   |

| 7. Peak Q-factor comparisons for single-ended and differential excitations         | 66   |

| 8. L and r values for Fig. 65                                                      | 69   |

| 9. Substrate parasitic parameter fit for single-ended and differential excitations | 69   |

| 10. Comparisons of published references with the differential symmetric inductor   | 70   |

| 11. Element and source values for the Colpitts oscillator                          | 72   |

| 12. Component values for the cross-coupled oscillator                              | 74   |

| 13. Comparisons between 8 nH symmetric and 4 nH conventional inductors             | 75   |

| 14. Comparison of cross-coupled oscillator performance for both inductors          | 76   |

# LIST OF SYMBOLS

| Co                | overall capacitance due to the overlap and interwinding capacitances                |

|-------------------|-------------------------------------------------------------------------------------|

| Cox               | oxide capacitance from the strip line to the SiO <sub>2</sub> /Si interface         |

| C <sub>si</sub>   | silicon capacitance from the strip line to the ground plane without the oxide layer |

| δ                 | skin depth                                                                          |

| ε <sub>r</sub>    | relative permittivity                                                               |

| ٤ <sub>reff</sub> | effective relative permittivity/dielectric constant                                 |

| f                 | frequency of operation                                                              |

| f <sub>peak</sub> | frequency at which the $Q$ peaks                                                    |

| f <sub>sr</sub>   | self-resonant frequency                                                             |

| G                 | inner gap between opposing groups of coupled strips of a spiral inductor            |

| l                 | total length of a microstrip line structure                                         |

| $\lambda_{g}$     | guided wavelength                                                                   |

| L                 | transmission line inductance                                                        |

| Ν                 | number of turns of a spiral inductor                                                |

| OD                | outer turn dimension of a rectangular spiral inductor                               |

| Q                 | inductor quality factor                                                             |

| Q <sub>peak</sub> | maximum inductor quality inductor value                                             |

| r                 | resistance due to a strip conductor                                                 |

| R <sub>si</sub>   | dissipation due to the conductive silicon                                           |

| ρ <sub>S</sub>    | metal sheet resistivity                                                             |

| ρ <sub>si</sub>   | silicon resistivity                                                                 |

| S                 | spacing between two microstrip lines                                                |

| t <sub>M</sub>    | upper metal thickness                                                               |

| t <sub>Mox</sub>  | oxide thickness between upper and lower metals used for an underpass                |

| t <sub>ox</sub>   | oxide layer thickness                                                               |

| t <sub>si</sub>   | silicon layer thickness                                                             |

| w                 | microstrip line width                                                               |

| w <sub>u</sub>    | microstrip line width for an underpass                                              |

### Chapter 1

### INTRODUCTION

### **1.1 Silicon Radio Frequency Integrated Circuits**

With the emergence of wireless communications systems such as personal communication services (PCS), wireless local area networks (WLANs), satellite communications, and the global positioning system (GPS), interest has focussed on radio frequency integrated circuits (RF ICs). In the 1980s, military applications drove the development of monolithic microwave integrated circuits (MMICs) forward by fabricating passive and active circuit elements on the same semi-insulating gallium arsenide (GaAs) substrate [1]. Compared with discrete and hybrid designs [2], the monolithic approach offers low cost, improved reliability and reproducibility, small size and weight, broadband performance, and circuit design flexibility. Disadvantages of the monolithic approach, such as process difficulties, low yields and poor performance, have largely been overcome [3]. The consumer electronics market favours silicon (Si) technology for its lower cost, higher yield, and the potential for mixing analog and digital circuits. Silicon bipolar and BiCMOS technologies now offer performance comparable with GaAs in the low GHz frequency range [1].

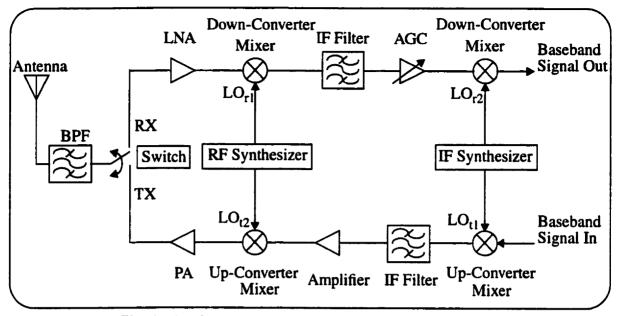

Figure 1 shows the RF front-end architecture for a heterodyne transceiver, where filters, amplifiers, mixers, and oscillators are needed for implementation. Inductors can be used in all stages of an RF IC for the input/output matching circuitry and passive filters. They are also convenient loads for active circuits, such as amplifiers and mixers, where lower noise performance and 1-3 V supply voltages may be realized. However, implementing the inductor on-chip has been regarded as an impractical task because of excessive substrate capacitance and substantial resistive losses due to metallization and the conductive silicon substrate, which degrade the overall performance of the circuit. Hence, all inductive components were integrated off-chip until, in 1990, planar inductors were demonstrated to be feasible in modern silicon technologies [4].

Fig. 1. RF front-end: heterodyne transceiver architecture.

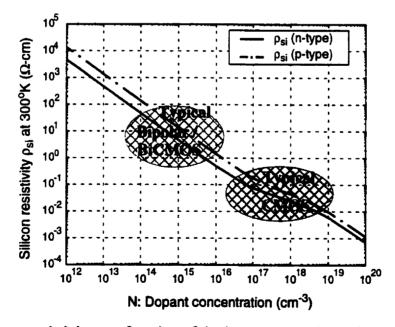

Compared with GaAs, on-chip inductors on silicon substrates have poorer performance simply because of the low substrate resistivity. Depending on the dopant concentration of the silicon wafer, the silicon resistivity can be as low as 0.01  $\Omega$ -cm for CMOS and 1  $\Omega$ -cm for bipolar, as illustrated in Fig. 2. For current bipolar and BiCMOS technologies, the typical silicon resistivity ranges from 1 to 10  $\Omega$ -cm, and for CMOS, from 0.01 to 1  $\Omega$ -cm.

Fig. 2. Silicon resistivity as a function of doping concentrations of n-type (phosphorus) and p-type (boron) [5].

### **1.2 Microwave Monolithic Inductors**

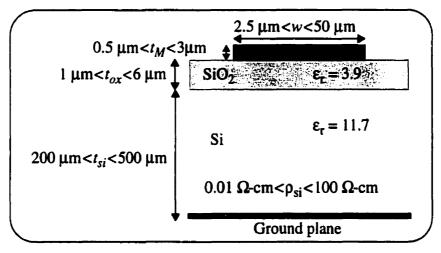

Passive inductors are implemented with high characteristic impedance microstrip lines fabricated on an insulating (SiO<sub>2</sub>) layer that lies on top of a silicon substrate and lower ground plane, as shown in Fig. 3. The typical range of values for each parameter is indicated. The silicon resistivity  $\rho_{si}$  must be accounted for in transmission line losses, whereas the oxide conductivity is on the order of 10<sup>-13</sup> S/m, and hence is considered negligible. Because of finite  $\rho_{si}$  and narrow strip width, design guidelines for MMIC structures are not found in the literature, contrary to established design guidelines for MICs [6, 7, 8, 9] for which the fields are in the quasi-TEM (transverse electromagnetic) mode [10]. This will be considered in Chapter 2.

Fig. 3. Microstrip line on silicon with a typical range of parameter values.

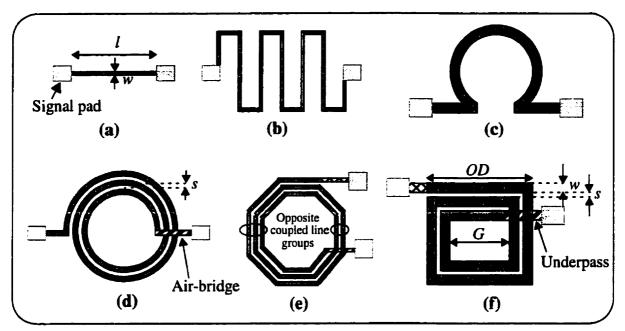

Figure 4 shows some planar inductor designs. The single microstrip line, meander, and single loop inductors provide inductances up to 0.5 nH and are seldom used. The meander inductor is designed to conserve chip area, but a better approach is to wind the microstrip line in a spiral, as shown in Fig. 4 (d), (e), and (f). Mutual coupling resulting from the closely spaced lines adds to the self-inductance of the transmission line, increasing the overall inductance. However, because of practical restrictions in the mask making process, the circular shape is implemented as an octogonal or a hexagonal spiral. Typically, inductances up to 20 nH are realized on-chip with spiral configurations. The rectangular spiral is the most

Fig. 4. Monolithic inductor configurations: (a) Microstrip line, (b) Meander line, (c) Single loop, (d) Circular spiral, (e) Octogonal spiral, (f) Rectangular spiral.

commonly used design due to its layout simplicity, however, higher losses are obtained compared with a circular layout, i.e., for equal inductances, as high as a 10% increase in the metallization loss results [11]. Its parameters include the outer dimension OD, the strip width w, the spacing between lines s, the number of turns N, and the gap between opposing groups of coupled lines G. The inner turn is connected to the outer circuitry by an underpass, routed via a lower level metal, or an air-bridge.

A coil or solenoid is the most familiar inductive component; thus the design of a planar spiral inductor may seem odd at first. Figure 5 illustrates the magnetic field lines for a coil, a planar solenoid, and the rectangular spiral. Closely spaced windings of the coil provide flux linkages on the top and bottom windings, and the flux lines pass through the middle of the coil. The same idea applies to the planar solenoid, but this design is not suitable for monolithic integration [12]. For the rectangular spiral, groups of coupled lines are located on the same plane, and the flux lines pass through the substrate layers, which results in greater inductance values compared with the planar solenoid.

Fig. 5. Magnetic field lines for (a) an air coil, (b) a planar solenoid, and (c) a planar rectangular spiral inductor.

### **1.3 Purpose and Organization of this Thesis**

The purpose of this thesis is to study the behavior of microstrip line structures on silicon in order to model monolithic inductors as equivalent electrical circuits and to design higher quality inductors for enhancing the performance of RF circuits. Chapter 2 provides an in-depth analysis of propagation issues for Si MMIC technology. This introduces the RF engineer to the design considerations for microstrip elements on a silicon substrate. Illustrations of various line parameters as a function of silicon resistivity and frequency will be presented to support theoretical predictions. A lumped element model is proposed for the single microstrip line, which is compared with numerical simulation results from commercial electromagnetic simulators.

Chapter 3 focusses on the modeling of spiral inductors in silicon technologies. A new inductor model and lumped element parameter extraction technique, based on the single microstrip line case, is compared with experimental and simulated results.

Present monolithic inductors can achieve a maximum Q-factor of 10, posing a limitation for narrowband circuits. Various Q enhancement and chip area reduction techniques have been proposed in the literature, as described in Chapter 4. A closer look at differential symmetric circuits that integrate spiral inductors leads to a differentially excited inductor instead of a single-ended layout where one end of the port is grounded. The differential configuration provides a higher Q (up to a 50% increase in the peak Q) by lowering the substrate parasitics which degrade the inductor performance without altering the fabrication process. A symmetric inductor is also presented. Measured and simulated inductor Q-factors agree to within 10%. To demonstrate the advantages and improvement in performance associated with a differential excitation of a symmetric inductor versus single-ended conventional asymmetric spiral inductors, the performance of single-ended and differential Colpitts oscillators at 2 GHz are compared.

### Chapter 2

### SILICON MICROSTRIP STRUCTURE CHARACTERISTICS

The first section of this chapter introduces the electromagnetic theory behind a microstrip line on a silicon substrate for which different propagation modes are defined. Lumped pi-type equivalent circuits for single and coupled microstrip lines are reviewed. The last section of this chapter will show how the propagation modes can be related to a lumped element equivalent circuit.

### 2.1 Wave Propagation Modes

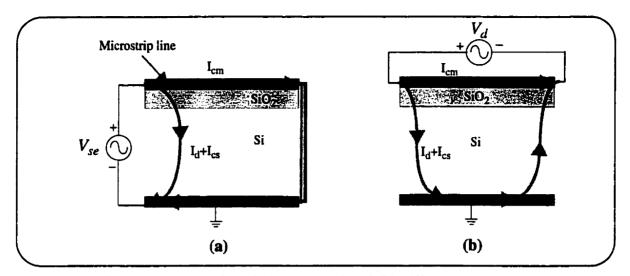

Studies of propagation on a microstrip line on a SiO<sub>2</sub>/Si substrate were first analyzed using a parallel-plate waveguide model [10, 13]. By observing the associated loss for various values of silicon resistivities and frequency ranges, three specific regimes were identified, each associated with a different propagation mode, as illustrated in Fig. 6 for the electric field distribution.

In Fig. 7, these three regimes are shown in a resistivity-frequency mode chart for typical oxide and silicon thicknesses. The regimes are defined as follows:

1) When the product of frequency and silicon resistivity is high, the silicon substrate

Fig. 6. Electric field distribution of (a) quasi-TEM, (b) slow-wave, and (c) skin-effect modes [10].

acts as a dielectric with a small dielectric loss tangent; the fundamental mode is close to the TEM mode and is therefore called a quasi-TEM mode. Its frequency range is defined for

$$f \ge \frac{1.5}{2\pi\rho_{si}\varepsilon_{si}}$$

(Hz) (1)

2) When the product of frequency and silicon resistivity is moderate, a surface wave propagates along the transmission line at the  $SiO_2/Si$  interface with a propagation velocity smaller than in the previous case. This is the slow-wave mode for which

$$f \le \frac{0.3}{\left(\frac{1}{f_s} + \frac{2}{3f_\delta}\right)}$$

(Hz) (2)

where  $f_s = \frac{t_{ox}}{2\pi t_{si} \varepsilon_{si} \rho_{si}}$  (Hz) and  $f_{\delta} = \frac{\rho_{si}}{\pi \mu_o(t_{si})^2}$  (Hz);

3) When the product of frequency and silicon conductivity is large enough so that the silicon substrate acts as a lossy conductor or an imperfect ground plane, the fundamental mode is called the skin-effect mode (where the skin depth  $\delta = \sqrt{\rho_{si}/(\pi\mu_o f)}$  (m) is on the order of the silicon thickness, i. e.,  $\delta = 160 \ \mu m$  at 1 GHz for  $\rho_{si} = 0.01 \ \Omega$ -cm). This mode appears for

$$f \ge 0.4 f_{\delta} \text{ (Hz).} \tag{3}$$

Standard Si bipolar processes range in the slow-wave, transition region of the slowwave to quasi-TEM, and quasi-TEM modes in the 1 to 10 GHz frequency range. CMOS RF applications are well within the slow-wave and even in the skin-effect regimes.

Fig. 7. Resistivity-frequency mode chart for various oxide/silicon thicknesses.

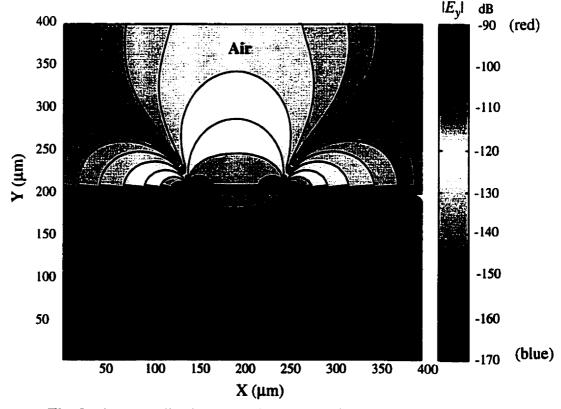

To show how the silicon substrate behaves with respect to its resistivity, vertical electric field maps for different  $\rho_{si}$  are given at 1 GHz. These field maps were extracted by a finite-difference time-domain (FDTD) 3D method [14]. The structure consists of a perfect electric conductor (PEC) sheet of 100  $\mu$ m width, oxide and silicon thicknesses of 5  $\mu$ m Fig. 8. FDTD space for a 100  $\mu$ m strip line. and 200 µm, respectively, and a 195 µm height

of free space, as shown in Fig. 8. For a 0.1  $\Omega$ -cm resistivity (Fig. 9), the silicon substrate is a lossy conductor, and most of the fields are in the oxide and air. A slow surface wave propagates along the line. The fields penetrate into the silicon as its resistivity increases, as shown in Fig. 10, where the propagation mode lies in the transition region between the slowwave to quasi-TEM modes and in Fig. 11, where it is in the quasi-TEM mode. Fringing fields are also present at the edges of the strip.

Fig. 9. Unnormalized vertical electric field for  $\rho_{si} = 0.1 \Omega$ -cm.

Fig. 11. Unnormalized vertical electric field for  $\rho_{si} = 10 \text{ k}\Omega$ -cm.

A two-dimensional numerical simulation using the spectral domain approach (SDA) [15, 16, 17] was used to extract the power in different layers, as shown in Fig. 12, for a single line and two coupled microstrip lines of 10  $\mu$ m width and 5  $\mu$ m spacing. (The SDA is a less computer intensive numerical method appropriate for 2D planar strip lines in a shielded box. Convergence was achieved with a box length of 10 mm with 4000 points and an air height greater than 1 mm.) All subsequent figures will show results for a 5  $\mu$ m thick oxide and a 350  $\mu$ m silicon layer. In the skin-effect mode, most of the fields penetrate the oxide layer and only slightly penetrate the silicon because of its high loss tangent (> 100 at 1 GHz). For the slow-wave regime, most of the active power is still in the oxide, but the rest is dissipated in the silicon by a conduction current. A large amount of reactive power is exchanged between substrate layers because of the movement of charges at the SiO<sub>2</sub>/Si interface [10]. Due to this energy transfer, a slower propagation velocity results. In the quasi-TEM regime, for a single microstrip line and evenly excited coupled lines, most of the energy is transmitted in the silicon substrate (as compared with the oxide) [10]. More electric field lines pass through the

Fig. 12. Unnormalized power in air, oxide and silicon for a single line, and even-mode and odd-mode excitations of two coupled microstrip lines ( $w = 10 \ \mu m$ ,  $s = 5 \ \mu m$ ) at 1 GHz.

conductive layer in the even-mode than in the single line case, whereas in the odd-mode, a substantial portion of the electric field is concentrated between the two strips [18, 19].

Figure 13 illustrates the slow-wave and quasi-TEM regimes for the range of silicon resistivities and frequencies of interest for RF ICs, given the effective dielectric constant  $\varepsilon_{reff}$  value of a 10 µm wide single microstrip line. As previously defined, a slow-wave propagates for certain silicon resistivity and frequency ranges, which results in higher effective dielectric constants. The quasi-TEM effective dielectric constant is around 5 (region shown in blue), while its value increases to reach a constant (11.6) in the slow-wave regime.

Figure 14 shows the transmission line parameters for single and coupled microstrip lines at a frequency of 1 GHz using the SDA method. Decreasing the line width causes less of the field to be contained in the lossy silicon substrate than in the oxide and the air, which reduces the value of the effective dielectric constant in the slow-wave region. This is also observed for an odd-mode excitation. Hence, as the width increases, the skin-effect is more

Fig. 13. Resistivity-frequency mode chart for  $Re[\epsilon_{reff}]$  for a 10 µm wide microstrip line.

Fig. 14. (a)  $\text{Re}[\varepsilon_{\text{reff}}]$  for three different line widths. (b)  $\text{Re}[\varepsilon_{\text{reff}}]$  for a 10 µm single line and coupled lines with 5 µm spacing. (c) Attenuation constant for single and coupled lines. (d) Real part and (e) imaginary part of the characteristic impedance for single and coupled lines.

pronounced and its region comes into effect earlier in terms of  $\rho_{si}$ . In the skin-effect regime, the silicon substrate acts as a lossy conductor, therefore reducing the effective height of the microstrip line from the actual ground plane. These arguments are further strengthened by the attenuation constant graph (Fig. 14 (c)). Attenuation is minimum in the slow-wave regime, and maxima occur for transitions from quasi-TEM to slow-wave and from slow-wave to the skin-effect regime. The highest attenuation is obtained at the transition to the quasi-TEM mode because of the dominant displacement current in silicon [10], and in the skin-effect region where the attenuation is constant. Both effective dielectric constant and characteristic impedance are constant in the slow-wave regime. The real part of the characteristic impedance follows the curves of the power flow in air, as shown in Fig. 12, whereas the reactive component is similar to the reactive power in the silicon layer.

For typical RF applications, it has been shown that due to the silicon resistivity value and frequency of operation, the slow-wave propagation mode and transitions between quasi-TEM and skin-effect modes are excited. This demonstrates the importance of the process chosen for the design of monolithic inductors. The influences of these propagation modes will be described throughout this chapter.

### 2.2 Lumped Circuit Modeling

For RF design, representation of microstrip lines by an equivalent circuit is needed in circuit simulators. Physical/electrical behaviours of monolithic inductors are translated into lumped element equivalent circuit models. The microstrip line is the simplest physical layout for a planar inductor for which an equivalent circuit is determined. This single microstrip line circuit model can also be applied to spiral inductors which consist of groups of coupled strips.

#### 2.2.1 Single Microstrip Line Modeling

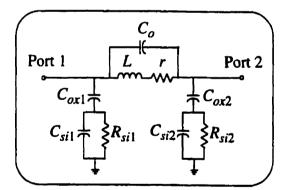

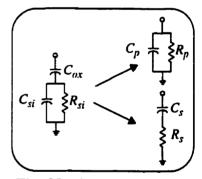

The electrical behaviour of a transmission line can be approximated over a range of frequencies by a lumped element equivalent circuit model. For a microstrip transmission line fabricated in silicon technology, an appropriate equivalent circuit is shown in Fig. 15, where L is the inductance of the line, and r is the series resistance mainly due to conductor losses. It is a frequency dependent element which accounts for the edge, proximity, and skin effects [20] on the current flow, and for the conductive silicon substrate [10], due to the current flow parallel to the strip current that is induced in the substrate. Induced eddy currents are attributed to the proximity effect [21]. The shunt parasitics result from a combination of capacitances, involving the insulating layer of silicon dioxide ( $C_{ox}$ ), the underlying substrate ( $C_{si}$ ) and its dissipation ( $R_{si}$ ) [10]. For an electrically short microstrip line where  $l < \lambda_g/10$ , a single  $\pi$ -section equivalent circuit (Fig. 15) is sufficient, whereas for a longer line, a distributed model should be used.

Fig. 15. Microstrip line equivalent circuit.

### 2.2.2 Spiral Inductor Modeling

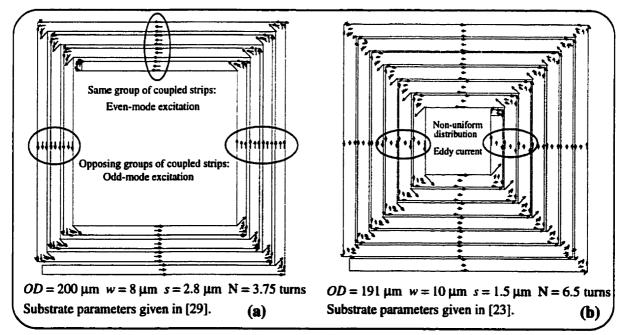

A spiral inductor consists of groups of coupled microstrip lines. Modeling the spiral requires knowledge of the currents flowing on the conductor. The current is a time varying component and flows continuously along the spiral. Currents on the same group of coupled strips flow in the same direction, which results in an even-mode excitation for the adjacent strips, as shown in Fig. 16 (a). This holds when the total length of the spiral is less than a quarter of the guided wavelength (where the inductor is self-resonant) and there is a negligible phase shift in the signal voltage or current. Currents on opposing groups of coupled strips flow

Fig. 16. Surface current flow for spiral inductors of (a) 3.75 turns and (b) 6.5 turns at 1 GHz.

in different directions, as in Fig. 16 (a), and hence, the odd-mode is excited. Also, the effect of the air-bridge or underpass can disturb the current distribution on the upper metal layer of the spiral, depending on the separation between the two metal layers [22]. As shown in Fig. 16 (b), decreasing the inner gap of the spiral causes a non-uniform current distribution. This current crowding effect is due to induced eddy currents on adjacent strips in the same group and in inner turns, which degrades the total inductance and increases the series resistance [23, 24].

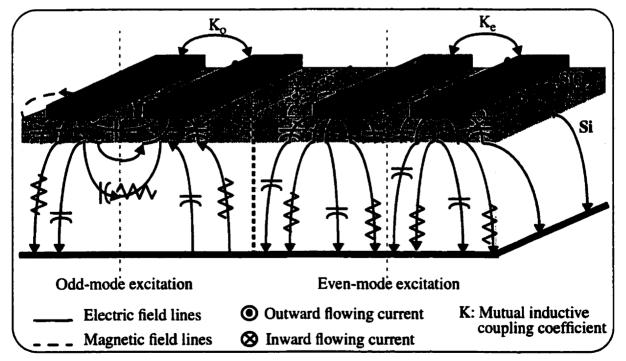

Figure 17 illustrates the electromagnetic field lines and how they influence the transmission line parameters for both odd and even-modes. In the latter case, both currents on adjacent strips flow in the same direction, which results in a positive mutual inductive coupling  $K_e$ , thereby increasing the total inductance. For silicon MMICs,  $K_e$  typically ranges from 0.5 to 0.8 [21]. Only the electric fields from the strips to the ground plane are present. Therefore, tighter spacing increases the inductance and decreases the substrate capacitance because of reduced electric fringing field lines. For an odd-mode excitation, currents flow in the opposite direction, which results in electric field lines between the strips through the air, oxide and silicon layers. Moreover, negative mutual inductive coupling  $K_o$  degrades the total inductance. Hence, for a spiral inductor, a substantial gap (G > 5w) must separate opposing groups of coupled strips [24, 25]. In conclusion, a spiral inductor can have excitations of

Fig. 17. Electromagnetic field lines and line parameters for two coupled lines for odd- and even-mode excitations.

mixed modes, making it difficult to understand and model.

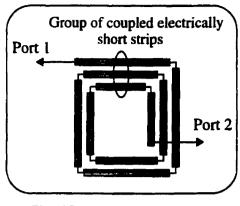

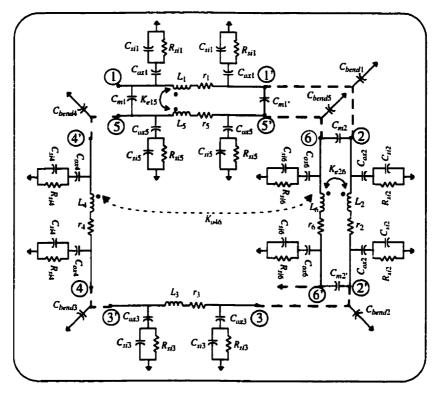

The spiral inductor can be considered to be a series of electrically short microstrip lines (Fig. 18) connected by mutual inductive coupling coefficients, interwinding (line-to-line) capacitances, and added parasitics due to the bends (considered negligible:  $C_{bend} < 1$  fF and  $L_{bend} < -0.05$  nH [26]) [25, 27]. Added capacitance due to the overlap between the turns of the spiral and the center-tap underpass or cross-over should also be taken into account. A more

Fig. 18. Simplified spiral inductor layout.

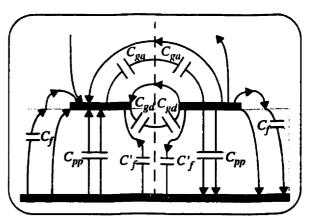

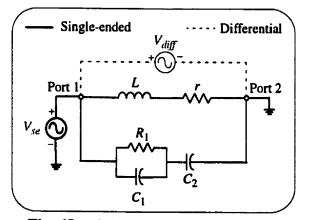

common representation of a spiral inductor is a compact model, shown in Fig. 19, which is derived from a single microstrip line equivalent circuit. Here, L and r represent the total inductance and resistance of the inductor, respectively. Shunt parasitics model the outer winding at Port 1, and the inner winding at Port 2. Using a conventional spiral inductor results in an asymmetry in the layout, which is represented by two sets of substrate parasitic values [25].  $C_o$  represents the overall line-to-line capacitance resulting from the combination of interwinding and overlap capacitances.

Fig. 19. Compact lumped element inductor model.

### **2.3 Inductor Quality-Factor**

The performance of an inductor is measured by its quality-factor (Q). It is defined as the ratio of the energy stored to the total dissipation per cycle for a sinusoidal excitation [28]:

$$Q = 2\pi \cdot \frac{\text{energy stored}}{\text{energy lost per cycle}} = \omega \cdot \frac{\text{energy stored}}{\text{average power loss}}.$$

(4)

From a circuit point of view, other interpretations of Q can be used, such as those from the -3 dB bandwidth at the angular resonant frequency ( $\omega_o$ ) or the rate of change of the phase shift at resonance, defined as follows:

$$Q = \frac{\omega_o}{\Delta \omega_{3dB}} \tag{5}$$

$$Q = \frac{\omega_o}{2} \cdot \frac{d\phi}{d\omega} \Big|_{\omega_o}.$$

(6)

For the case of an inductor, only the energy stored in the magnetic field is considered, whereas energy stored in the electric field, due to parasitic capacitances, counteracts the inductive energy.

For a series L-r circuit connected as a one-port, the Q-factor is defined as

$$Q = \frac{\omega L}{\operatorname{Re}[Z_{in}]} = \frac{\omega L}{r}$$

(7)

and for a parallel  $L_p$ - $r_p$  circuit,

$$Q = \frac{1}{\operatorname{Re}[Y_{in}] \cdot \omega L_p} = \frac{r_p}{\omega L_p}$$

(8)

valid until the inductor's first self-resonance, where  $Z_{in}$  is the input impedance and  $Y_{in}$  is the input admittance of the one-port structure. A resonance occurs when the peak magnetic energy equals the peak electric energy or  $X_L = -X_C$ , where C is the total circuit capacitance, and the resonant frequency is

$$f_{sr} = 1/(2\pi\sqrt{L \cdot C})$$

(Hz). (9)

In this case and beyond the self-resonant frequency, no net magnetic energy is available.

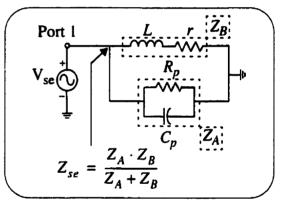

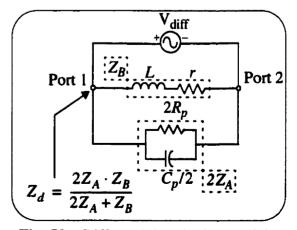

Closed-form expressions approximating the monolithic inductor Q-factor are given by Yue and Wong [29] by considering the circuit in Fig. 20, where  $C_p$  and  $R_p$  replace the substrate shunt parasitics  $C_{ox1}$ ,  $C_{si1}$  and  $R_{si1}$  in Fig. 19, and are thus frequency dependent, and by

Long and Copeland [25]. Different estimations of Q-factor expression are presented in [30]

and [31] and their range of validity is discussed. For this thesis, Eq. (8) is mainly used.

Fig. 20. Equivalent 1-port model.

### **2.4 Parameter Extraction Methods**

This section describes how inductor parameter values for the lumped elements are obtained. The first method does not require knowledge of the physical layout of the structure. From the two-port S-parameters, given either by measurement or simulation, series and shunt impedances for the compact model of Fig. 19 are derived. The second method consists of determining analytically the L, R, and C component values from the physical layout and fabrication process specifications.

### 2.4.1 Parameter Extraction from Two-Port Results

A microstrip inductor is a two-port element. The S-parameters are determined from simulation or measurement. Series inductance L and resistance r in the compact model (see Fig. 19), are first derived at low frequencies from the one-port input impedance of the two-port network, as

$$Z_{in} = Z_{11} - \frac{Z_{12} \cdot Z_{21}}{Z_{22}} (\Omega).$$

(10)

Figure 21 gives an example of the real and imaginary parts of the input impedance for a spiral inductor derived from measured two-port S-parameters [32]. At low frequencies  $(IX_C I >> IX_L I)$ , r is given by  $Re[Z_{in}]$ , and L as  $Im[Z_{in}]/2\pi f$ ; they are 7.7  $\Omega$  and 7.5 nH, respectively. As the frequency increases, inductive reactance increases and capacitive and resistive parasitics come into play, causing a resonance near 6.3 GHz, when the resistive part of the input impedance is maximum and the reactance is zero. Beyond resonance, the

Fig. 21. Measured real and imaginary parts of the input impedance of a spiral indutor  $(N=5, w=8 \ \mu m, s=2.8 \ \mu m).$

reactance is negative, and hence the inductor behaves as a capacitor.

Using an optimizer to fit the measured and simulated S-parameters, approximate values for shunt parasitics and overall capacitance  $C_o$  are obtained, as shown in Fig. 22. Data for a CMOS 4.25 turn spiral inductor are fit to a frequency range of 0.5 to 6 GHz (below the self-resonance). The shunt parasitic capacitances are lower at the output port (Port 2) because the inner turn of the spiral is shorter in length than the input port (Port 1) outer turn. This results in an asymmetry in the parameter values for  $C_{ox}$ ,  $C_{si}$ , and  $R_{si}$  in the model.

Fig. 22. Parameter fit circuit model for measured and (simulated) CMOS spiral inductor.

The previous method involved fitting the parameter values to a set of two-port results over a range of frequencies, using a computer. Another way is to translate the two-port Sparameters to a set of lumped element values at each frequency point. The S-parameters are converted into the propagation constant  $\gamma$  and the characteristic impedance  $Z_o$  of a transmission line, from which the lumped elements (*L*, *r*, *C<sub>p</sub>*, *R<sub>p</sub>* and *C<sub>o</sub>*) are derived [33]. Figure 23 summarizes the procedure in a flowchart. Simulators such as Sonnet-em provide  $\varepsilon_{\text{reff}}$  and  $Z_o$  values for both ports which can be applied to the method of Fig. 23 by directly extracting the component values per unit length.

$$\begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \rightarrow \begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} \cosh \gamma l & Z_o \sinh \gamma L \\ \frac{\sinh \gamma L}{Z_o} & \cosh \gamma L \end{bmatrix} \rightarrow (\gamma, Z_o) \rightarrow \underbrace{\begin{array}{c} C_o \\ Port \ 1 \\ \hline C_p \\ \hline C_p$$

Fig. 23. Parameter extraction by the transmission matrix .

#### **2.4.2 Analytical Parameter Extraction**

This section provides a review and a discussion of the extraction methods used for each lumped element parameter, as well as new concepts.

#### a) Inductance

Inductance is defined as the ratio of the total flux linkages to the current to which they link [34]. Mutual inductance caused by the magnetic interaction between two currents adds to the self-inductance. Depending on the configuration of the conductors, the inductance may be expressed as a function of the physical dimensions, as for an N-turn coil or solenoid [35]. Greenhouse derived the total inductance of a planar rectangular spiral inductor [36], based on the closed-form inductance formulas for the self and mutual inductances of rectangular conductors published by Grover [37], resulting in an inaccuracy of less than 5% compared with measurements. However, these inductances were derived assuming a thick substrate ( $w \ll$  substrate height) and a static value which does not take into account the electrical length of the spiral inductor at high frequencies where the inductor resonates. Krafesik and Dawson [38] approached these effects by including a negative mutual inductance when the spiral outer diameter is comparable to the ground plane distance, and taking into account propagation delay around the spiral. The experimental results agreed to within 5%.

Other authors have provided crude estimates of the total spiral inductance with closedform expressions [39, 40]. Mohan *et al.* [41] obtained an inductance expression for square spirals with tight line spacings (s < w/2), which does not take into account the metal thickness. It has been shown that the inductance matrix can be obtained from the free space capacitance matrix  $[C_{air}]$  with respect to the ground plane, defined as  $[L] = \varepsilon_o \mu_o / [C_{air}]$  [42]. This definition can be useful if a full-wave or 2D method gives the capacitive parameter values in matrix form. Full-wave methods can also be applied to obtain more accurate results [31].

However, Greenhouse's method can be easily implemented in a computer program and can be modified for any rectangular layout geometry. Therefore, this method will be used throughout this thesis.

#### **b)** Capacitance

The capacitance C relates the ratio of the total charge to the potential difference between two conductors. For two parallel conducting plates, C is expressed as a function of the physical dimensions and substrate layer permittivity as

$$C = \frac{\varepsilon_o \varepsilon_r \cdot w \cdot l}{d}$$

(F) (11)

where d is the separation between the two plates, assuming a uniform current distribution on the plates and  $d \ll w$  and l [43]. For an MMIC microstrip line where w is on the order of 2 to 50 µm, which is comparable to the oxide thickness, and is much smaller than the silicon thickness (200 - 500 µm), these assumptions are no longer valid.

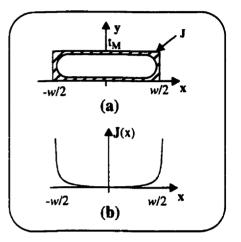

As illustrated in Fig. 24, electric field lines are non-uniform; hence, fringing fields must be taken into account. The total capacitance consists of  $C_{pp}$ , the parallel plate capacitance, and of  $C_f$  for the fringing capacitance. To provide accurate capacitance values, several approaches have been used. For computational efficiency, a two-dimensional numerical analysis technique is often used under static assumptions. For

Fig. 24. MMIC microstrip line with electric fields shown.

coupled strips, odd and even-mode capacitances have been calculated [44, 45], and for multiconductor strips, capacitance matrices are obtained [46, 47, 48, 49, 42]. Basis functions for the non-uniform current, which model the surface edge effect on the charge density for a microstrip line, are used to enhance the accuracy of solutions [50]. Other methods, such as the boundary element method (BEM) [51], the finite-difference (FD) [52], or the measured equation of invariance (MEI) [53], have been used. (The references do not provide an exhaustive list of publications.)

The overlap capacitance for the underpass  $C_u$  may be approximated using (11)

$$C_{u} = \frac{\varepsilon_{ox} w w_{u}}{t_{Mox}}$$

(F) (12)

where  $t_{Mox}$  is the separating distance between the upper and lower metals used for the underpass in the oxide layer, and  $w_u$  is the line width of the underpass. Because of additional

stray fields surrounding the overlap, it has been shown that  $C_u$  is increased by a factor of 1.5 to 1.7 relative to (12) [54].

The interwinding capacitance is the line-to-line coupling capacitance between adjacent conducting strips. Due to differences in phase between the voltage on each strip, the interwinding capacitance is the odd-mode coupling capacitance in the substrate and air. Figure 25 illustrates the electric field lines and associated odd-mode capacitances for two coupled microstrip lines. The coupling capacitances,  $C_{gd}$  and  $C_{ga}$ , can be calculated

Fig. 25. Odd-mode capacitances for two coupled microstrip lines.

from the corresponding coupled stripline geometry filled with substrate dielectric and air, respectively [55]. This method is efficient for two coupled microstrip lines only. Mutual coupling capacitances can be also obtained using a full-wave analysis technique for any arbitrary number of conductors [31, 46].

The overall capacitance  $C_o$  in shunt with the series inductance and resistance is a combination of interwinding and the underpass or bridge capacitances. This will be discussed in Chapter 3.

#### c) Resistance

From Ohm's law, the resistance of a conductor is defined to be the ratio of the electromotive force to the strength of the current that it produces. The DC resistance depends on the nature of the conductive material and the temperature [56].

### Series Resistance due to Metallization

Resistance is defined by the current distribution on the mictrostrip line, and in the case of silicon, also by the conduction current inside the silicon substrate. Resistance due to the strip line varies with frequency in a complicated manner. They are four factors to take into account: 1) DC, 2) Edge effect, 3) Proximity effect, and 4) Skin-effect [20].

At low frequencies, approaching DC, the current is uniformly distributed over the conductor. The DC resistance  $R_{dc}$  of a microstrip line is determined from the sheet resistivity

$\rho_s$  of the metal. Typical values for aluminum and aluminum alloys are on the order of 30 m $\Omega$ - $\mu$ m.

As the frequency increases (low MHz range), the current distribution changes due to the induced electric field in the conductor (produced by excess charges). The current concentrates at the sharp edges of the conductor. A reduction of the effective conductor crosssection increases the resistance [20]. Proximity effect also takes place when a nearby conductor carrying a time-varying current induces a magnetic field on the conductor which causes a current to flow in the opposite direction [21, 57].

At higher frequencies (in the range of MHz or GHz, depending on the strip line geometry), for MMIC lines, where w/h < 0.1 (*h* is the total substrate thickness, i.e.,  $t_{ox}+t_{si}$ ), the microstrip line is far enough from the ground plane such that the current is concentrated on the surface of the conductor as in the case of an isolated conductor, as illustrated in Fig. 26 (a). Hence, the ground plane resistance can be considered negligible [58].

Fig. 26. Current distribution for an MMIC microstrip line.

At these higher frequencies, skin-effect takes place because for MMIC strip lines, the width is

comparable to the metallization thickness (0.5 to 3  $\mu$ m typical), and the skin depth value  $(\delta = \sqrt{\rho_s/(\pi\mu_o f)})$  (m)) approaches that of the metal thickness: for  $\rho_{sAl}$  given above,  $\delta = 2.578/(\sqrt{f})$  ( $\mu$ m), where *f* is in GHz. Also, due to skin-effect, the current crowds at the edges of the strip. However, all three effects (edge, proximity, and skin-effect) are present and it is difficult to identify the contribution of each one on the total current distribution [20]. Figure 26 (b) shows the current distribution on a microstrip line at high frequencies. Exact calculation of the frequency dependent resistance requires the need of a full-wave method. For example, Waldow and Wolff investigated the skin-effect on rectangular conductors at higher frequencies using a variational approach [59, 60].

To quantify the total resistance at high frequencies without the use of a full-wave method, the resistance can be defined as having a DC and an AC component  $R_{ac}$  as

$$R = R_{dc} + R_{ac} = \frac{\rho_s \cdot l}{t_M \cdot w} + R_{ac} \quad (\Omega). \tag{13}$$

Several closed-form resistance approximations are found in the literature. Pettenpaul *et al.* [39] give an expression based on measured data for wide strips ( $w > 50 \mu$ m), Eo and Eisenstadt [61] derive an expression assuming an exponentially decaying current function, and Sonnet-em uses a square root frequency dependence to account for the skin-effect [62].

For this thesis, the series resistance expression chosen for the strip line  $r_{sl}$  is based on [61], given as

$$r_{sl} = \frac{\rho_{sAl} \cdot l}{w \cdot \delta \cdot (1 - e^{-t_M/\delta})}$$

(Ω) (14)

which accounts for the metallization skin depth  $\delta$ . The  $\delta \cdot (1 - e^{-t_M/\delta})$  term is equivalent to an effective metal thickness  $t_{eff}$  [63]. However, Eq. (14) assumes that the skin-effect occurs from frequencies just above DC, which is not the case for narrow strip widths. To account for the skin-effect influence at a higher frequency, a transition frequency  $f_{se}$  is defined when  $\delta = t_M$ , which is also dependent on the  $t_M / w$  ratio. Hence, the resistance is normalized at a frequency  $f_{se}$  and the values below this frequency threshold is approximated by the DC resistance, as the following:

$$r_{sl} = \begin{cases} \frac{R_{dc}}{r_{se}} & f \leq f_{se} \\ \frac{R_{dc}}{r_{se}} \cdot \frac{t_M}{\delta \cdot (1 - e^{-t_M/\delta})} & f > f_{se} \end{cases}$$

(15)

where  $r_{se}$  is the resistance at  $f_{se}$  defined by (14). Another approximation is also proposed by Eo and Eisenstadt [61], for modeling the side wall current of microstrip lines.

The resistance  $r_{\delta}$  accounts for losses due to the longitudinal component of the conduction current in silicon. It is a function of the square of frequency [10] and dominates the inductor loss mainly as a function of  $\rho_{si}$  and *f*. It is approximated as

$$r_{\delta} \approx 3.5 \times 10^6 \cdot \frac{f^2 \cdot t_{si}^2}{\rho_{si}} \cdot l \quad (\Omega)$$

(16)

where f is in GHz.  $r_{\delta}$  was obtained by fitting Eq. (16) to the series resistance curves given by simulators. Hence, the total resistance becomes

$$r = r_{sl} + r_{\delta} (\Omega). \tag{17}$$

The accuracy of Eq. (17) will be illustrated through examples.

As the silicon resistivity decreases ( $\rho_{si} \ll 0.1 \ \Omega$ -cm), the silicon acts as a lossy ground plane and its effect becomes dominant. For very low resistivities (< 0.1 m $\Omega$ -cm), the silicon can be considered as a lossy metal. Hence, the total resistance must take into account the resistance due to the silicon 'ground plane' because the strip is only on top of the oxide layer, such that the current distribution on the strip is mainly concentrated on the lower side close to the silicon 'ground plane'. The surface current on the ground plane is also concentrated under the strip so that the resistance of the ground place converges to  $r_{sl}$  at high frequencies and for  $w/t_{ox} \rightarrow \infty$  [58].

## Substrate Resistance due to Conductive Silicon

Similarly, computing the substrate resistance  $R_{si}$  is not an easy task. Full-wave methods that account for substrate resistivity are required. However, if the silicon capacitance is known, the following result is obtained from the resistance and capacitance definitions [64, 65]:

$$R_{si} = \frac{\varepsilon_{si} \cdot \rho_{si}}{C_{si}} \quad (\Omega).$$

(18)

### d) Temperature Dependence

An important aspect in designing RF circuits is the ability of the circuit to function within a broad temperature range (typically, -50 to 85°C). Metallization and substrate resistivities depend on temperature according to the following linear approximation:

$$\rho - \rho_o = \rho_o \alpha (T - T_o) \tag{19}$$

where  $T_o$  is a selected temperature,  $\rho_o$  is the resistivity at that temperature, and  $\alpha$  is the temperature coefficient [66]. From experimental results, it has been shown that for Al/Cu (98% Al),  $\alpha$  is around 0.34%/°C, whereas for a 15  $\Omega$ -cm silicon resistivity, it is 0.35%/°C [67]. As the substrate doping decreases, and hence a higher resistivity  $\rho_o$  ensues, a higher

temperature dependence is obtained, as seen from Eq. (19) [5]. An increase in the temperature results in an increase in the metal series resistance causing Q to decrease. The substrate resistance would, on the contrary, dominate the determination of Q at frequencies beyond the Q peak, and cause an increase in the Q. Nevertheless, for applications of inductors in silicon, the metallization resistance has the dominant effect on Q [67]. The inductance is not affected by temperature variation, and the substrate capacitance has a temperature coefficient of - 0.18%/°C [67], which can be considered negligible for MMIC microstrip structures because a 10% change in the substrate capacitance would cause less than a 5% decrease in the overall performance such as Q. Hence, for MMIC spiral inductors on a SiO<sub>2</sub>/Si substrate, it is the effect of temperature on the series resistance which should be considered.

## 2.5 Microstrip Line Simulation and Modeling

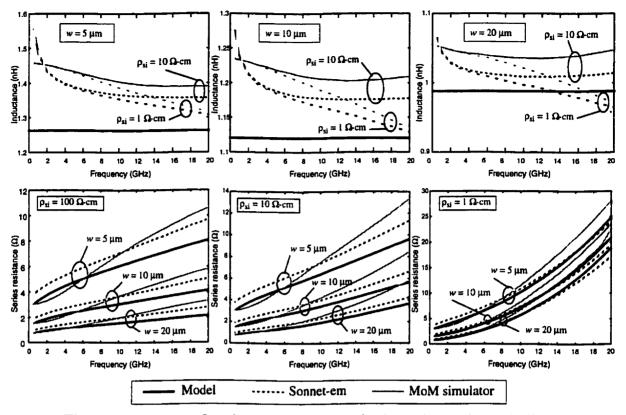

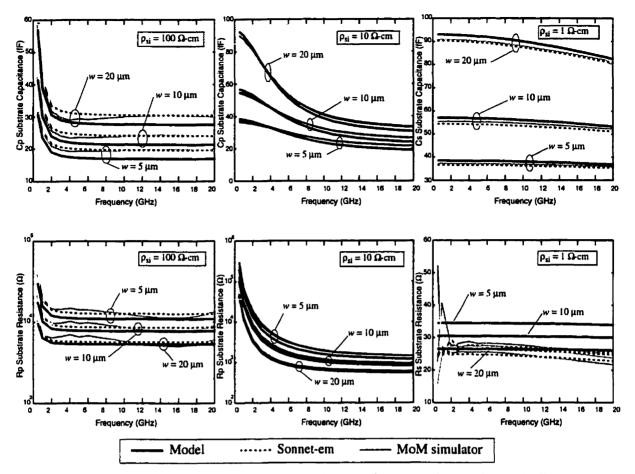

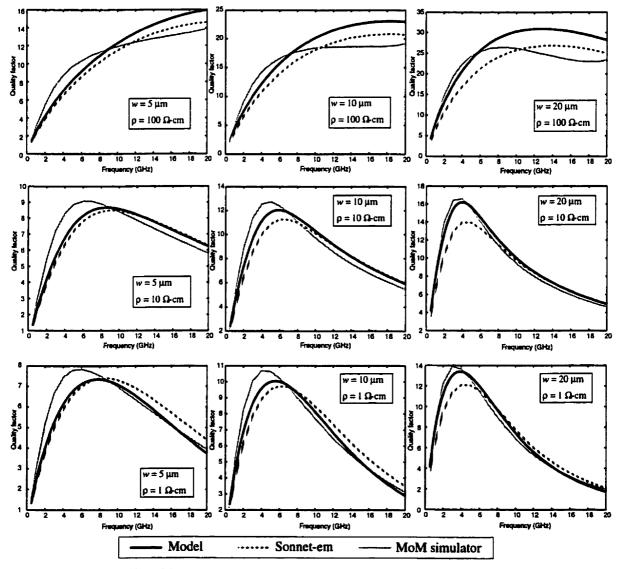

To verify what has been described throughout this chapter, various 1 mm long microstrip lines were simulated by two full-wave commercial electromagnetic simulators, Sonnet Software em and HP-EESof Series IV Momentum, referred to as the MoM (method of moment) simulator in this thesis, and an approximate model was also developed. Each simulator uses the method of moments in the spatial domain. Momentum uses a mixed potential integral equation [68], whereas Sonnet is based on an FFT [69]. Both use a rooftop expansion or basis functions for the current distribution. Results for line widths of 5, 10, and 20  $\mu$ m and for silicon resistivities of 1, 10, and 100  $\Omega$ -cm will be presented and discussed. The oxide and silicon thicknesses are 5  $\mu$ m and 350  $\mu$ m, respectively. The aluminum metal thickness is 2  $\mu$ m with a 30 m $\Omega$ - $\mu$ m resistivity.

### **2.5.1 Approximation Model**

The spectral domain technique was used to derive the substrate capacitances. For each substrate layer, the program was run for the particular substrate thicknesses: first, for that of the oxide from which  $C_{ox}$  was determined; and second, for that of the lossless silicon layer, where  $C_{si}$  and L were obtained. For ratios of  $t_{si}/t_{ox} > 50$ , the electric field distribution in the silicon layer does not change significantly whether a thin layer of oxide is present or not. For typical thicknesses (i.e.,  $t_{ox} = 5 \ \mu m$  and  $t_{si} = 300 \ \mu m$ ), this assumption holds. For this model, the line inductance value was approximated to be the same as the value for the silicon layer

alone because L depends on physical dimensions, and the difference is negligible (<1%) when compared with the structure's exact simulation. The program does not account for metal thickness. Other closed-form expressions could also be used, such as that of Greenhouse. The total series resistance r accounts for the skin-effect and the conductive silicon, defined in Eq. (17). Here,  $R_{si}$  was determined from  $C_{si}$  as in (18).

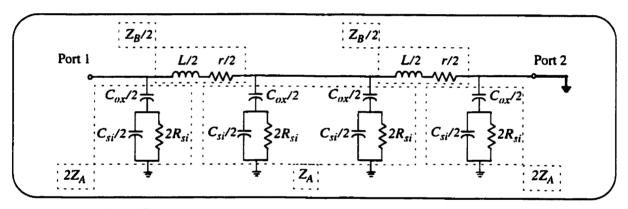

In the worst case, where  $w = 20 \ \mu m$  at 20 GHz, an effective relative permittivity of 13.6 was obtained. Hence the guided wavelength is 4.06 mm. For a lumped element equivalent circuit to hold for the microstrip line of 1 mm, a distributed model with at least three sections must be used, assuming that each section is smaller than one-tenth of the guided wavelength. For clarity, Fig. 27 shows a two-section distributed model. The series impedance and the shunt admittance are divided by the number of sections. To obtain the resulting Q, Port 2 is shorted, and the input impedance is determined as a function of  $Z_A$  and  $Z_B$ .

Fig. 27. Distributed model of a microstrip line with two sections.

## 2.5.2 Results

Table 1 compares the line inductance values obtained from the electromagnetic simulators and approximate expressions for  $\rho_{si} = 10 \ \Omega$ -cm. Only Greenhouse [36] and Pettenpaul [39] account for the metal thickness. Sonnet-em and Momentum give the highest values, differing by as much as 10% from the other methods.

| Methods         | L (nH)<br>(w=5 μm) | <i>L</i> (nH)<br>(w=10 μm) | <i>L</i> (nH)<br>(w=20 μm) |

|-----------------|--------------------|----------------------------|----------------------------|

| Sonnet-em       | 1.357              | 1.176                      | 1.009                      |

| Momentum        | 1.39               | 1.203                      | 1.035                      |

| Model: SDA      | 1.26               | 1.12                       | 0.988                      |

| Greenhouse [36] | 1.231              | 1.124                      | 1.003                      |

| Pettenpaul [39] | 1.231              | 1.123                      | 1.003                      |

| Lawton [70]     | 1.268              | 1.13                       | 0.991                      |

**Table 1.** Microstrip line inductance comparison for  $\rho_{si} = 10 \Omega$ -cm.

The inductance and series resistance (Fig. 28) are extracted from the simulated Sparameters using the method illustrated in Fig. 23. Simulated inductance curves show higher inductance values at low frequencies, an effect that is more pronounced using Sonnet-em (f < 4 GHz), which illustrate the limitations of the simulators. Moreover, the two simulators define the AC resistance differently, which results in different series resistance curves. Depending on the silicon resistivity and the frequency of operation, series impedances are different, mainly due to the conduction current in the silicon: r increases drastically as the frequency increases, and the line inductance decreases approximately linearly (<1%/GHz at 1  $\Omega$ -cm). Therefore, a reasonable assumption for the inductance value as a consant is verified. Taking into account the metal thickness for the inductance causes a slight error (a 5% difference for a 5 µm width, computed by the Greenhouse and Pettenpaul expressions). The low frequency series resistances are equivalent to the DC resistance. The model used for the resistance approximates the curve of Sonnet-em because the resistance expressions both depend on the square root of the frequency. For  $\rho_{si}$  equal to 100  $\Omega$ -cm, the conduction current in the silicon is considered negligible and does not affect the total resistance. At 10  $\Omega$ -cm, the conductive silicon effect is more pronounced at higher frequencies (> 10 GHz). In the slowwave mode ( $\rho_{si} = 1 \Omega$ -cm), the conduction current in the silicon is dominant, so that the total resistance depends mainly on  $r_{\delta}$ . Therefore, the resistance expression for the model, Eq. (17), is validated.