## **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality  $6^* \times 9^*$  black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

.

# High Voltage Circuits for Short Loop SLICs in a Low Voltage Submicron BiCMOS Technology

by

Mehran Aliahmad

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy Graduate Department of Electrical and Computer Engineering University of Toronto

© Copyright by Mehran Aliahmad 1998

# National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérence

Our file Notre rélérence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-41393-4

# High Voltage Circuits for Short Loop SLICs in a Low Voltage Submicron BiCMOS Technology

### Mehran Aliahmad

#### **Doctor of Philosophy, 1998**

#### Department of Electrical and Computer Engineering University of Toronto

#### Abstract

This thesis deals with the integration of short loop subscriber line interface circuits (SLIC) using a low voltage submicron BiCMOS technology. The high voltage front-end of the short loop SLIC was implemented in a 5V,  $0.8\mu$ m BiCMOS process. The use of a low voltage process allows the implementation of the SLIC's high voltage functions on the same chip with the rest of the high-density low-voltage circuits at much lower cost while achieving higher performance.

The short loop SLIC front-end presented includes all the required high voltage building blocks such as differential preamplifier, line drivers and power switch. Using a novel high voltage common-mode feedback circuit, the fully differential 30V preamplifier provides a wide bandwidth (more than 30MHz) with a power dissipation of only 10mW and an area of 0.1 mm<sup>2</sup>. Three different line drivers were also presented in this thesis, all capable of driving more than 30mA loop current while operating at supply voltages as high as 30V. The first line driver uses a pure CMOS process based on a quasi-current-mirror (QCM) class AB output stage and provides a bandwidth of 2 MHz with a power of only 25mW and an area of 0.3 mm<sup>2</sup>. A BiCMOS process is used in the second line driver resulting in improved performance and lower sensitivity to process variations. This line driver exhibits a bandwidth larger than 3MHz with 30mW power and 0.24 mm<sup>2</sup> area. A floating-current-mirror (FCM) PMOS output stage is used in the third line driver. This design is robust with respect to hot-carrier problems in NMOS devices and provides a very well controlled quiescent current. A bandwidth of 3.8 MHz is achieved with only 18 mW of power and 0.34 mm<sup>2</sup> of area.

# Acknowledgments

I would like to express my sincere gratitude to Professor C.A.T. Salama for his insightful guidance and invaluable assistance throughout the course of this work.

I am also indebted to Mr. J. Kwan from Nortel for his technical advice and help in implementing the chips.

My sincere thanks to Jaro Pristupa for his assistance, friendship and trust. My appreciation extends to all the staff and students in the Microelectronic Research Laboratory including Dana Reem, Anthoula Kampouris, Jeewika Ranaweera, Mehrdad Ramezani and Tirdad Sowlati for all their help. I am specially grateful to Luigi Depede for his feedback on the thesis manuscript.

I would like to thank my friend, Ali Sheikholeslami, who kept me company with his constructive discussions and cheerful chats, and the rest of our gang, Amir Aghdam, Rashid Kohan and Shahin Hashtrudizad who were always there for me.

A special word of thanks to my parents and my brothers who have been a constant source of support and encouragement.

And to my wife Pouneh, thank you for your patience, support and love.

This work was supported by the Natural Sciences and Engineering Research Council of Canada, Nortel and Micronet.

# **Table of Contents**

•

| CHAPTER 1 Introduction1                                 |

|---------------------------------------------------------|

| 1.1 Subscriber Loop Interface Circuits (SLIC)           |

| 1.2 Short Loops and Their Applications6                 |

| 1.2.1 Fiber-In-The-Loop (FITL)7                         |

| 1.2.2 Hybrid-Fiber-Coax (HFC)10                         |

| 1.2.3 Wireless Local Loops (WLL)11                      |

| 1.3 High Voltage Integrated Circuits Processes12        |

| 1.4 Previous work on SLICs15                            |

| 1.5 Objectives and Outline of the Thesis17              |

| CHAPTER 2 Short Loop SLIC System20                      |

| 2.1 Introduction                                        |

| 2.2 Short Loop SLIC Requirements                        |

| 2.3 Proposed Architecture for a Short-Loop SLIC         |

| 2.3.1 Preamplifier Design24                             |

| 2.3.2 Common-Mode Feedback Circuit                      |

| 2.3.3 Line Drivers                                      |

| 2.4 Summary                                             |

| CHAPTER 3 BiCMOS Compatible High Voltage Device Design  |

| 3.1 Introduction                                        |

| 3.2 BATMOS-5 Process                                    |

| 3.3 BATMOS-10 Process                                   |

| 3.4 High Voltage Device Structures                      |

| 3.5 Experimental Device Characterization and Modeling42 |

| 3.6 Other Components                                    |

| 3.7 Summary                                             |

| CHAPTER 4 High Voltage Circuits Design55                |

| 4.1 Introduction55                                      |

|                                                     | Page |

|-----------------------------------------------------|------|

| 4.2 Preamplifier Design                             | 56   |

| 4.2.1 Common-Mode Feedback Circuit                  | 59   |

| 4.2.2 Implementation and result                     | 62   |

| 4.3 Power Supply Switch                             | 64   |

| 4.3.1 Experimental results                          | 66   |

| 4.4 Line Driver Design                              | 68   |

| 4.5 CMOS Line Driver with QCM Output Stage (CQCM)   | 71   |

| 4.5.1 Circuit Description                           | 71   |

| 4.5.2 QCM Output Stage                              | 73   |

| 4.5.3 Device Parameters and Compensation            | 76   |

| 4.5.4 Gate Protection                               | 77   |

| 4.5.5 Implementation and Results                    | 79   |

| 4.6 BiCMOS line driver with QCM output stage (BQCM) | 84   |

| 4.6.1 Circuit Description                           | 84   |

| 4.6.2 Device Parameters                             | 87   |

| 4.6.3 Compensation                                  | 87   |

| 4.6.4 Implementation and Results                    | 91   |

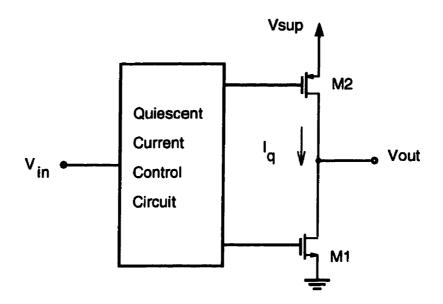

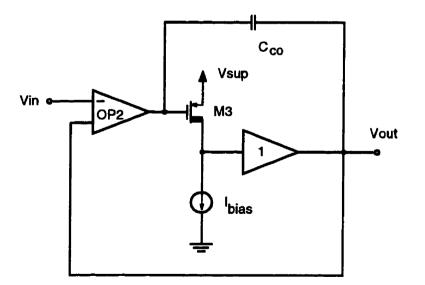

| 4.7 Floating-Current-Mirror Line Driver (FCM)       | 96   |

| 4.7.1 Circuit Description                           | 96   |

| 4.7.2 Device Parameters and Biasing                 | 101  |

| 4.7.3 Internal Opamps                               | 103  |

| 4.7.4 FCM Stage Frequency Response and Compensation | 107  |

| 4.7.5 Experimental results                          | 115  |

| 4.8 System Integration                              | 120  |

| 4.9 Summary                                         | 120  |

| HAPTER 5 Conclusions                                |      |

| PPENDIX A High Voltage Device Library               |      |

| A.1 Device Layouts                                  |      |

| A.2 Using mask layers in BATMOS-5 and BATMOS-10     | 131  |

| A.3 Models.                                         |      |

# **List of Figures**

|                                                                                   | Page       |

|-----------------------------------------------------------------------------------|------------|

| Fig. 1.1: Subscriber loop connecting the subscriber to the central office         | 4          |

| Fig. 1.2: A typical telecommunication channel                                     | 4          |

| Fig. 1.3: Schematic of a central office SLIC                                      | 5          |

| Fig. 1.4: Cumulative distribution of existing loops in terms of length [6]        | 7          |

| Fig. 1.5: Schematic of a fiber-to-the-curb system                                 | 9          |

| Fig. 1.6: Estimated initial cost of the installation of FTTC systems per customer | 9          |

| Fig. 1.7: Schematic of a hybrid-fiber-coax system                                 | 10         |

| Fig. 1.8: Schematic of a wireless local loop system                               | <b>1</b> 1 |

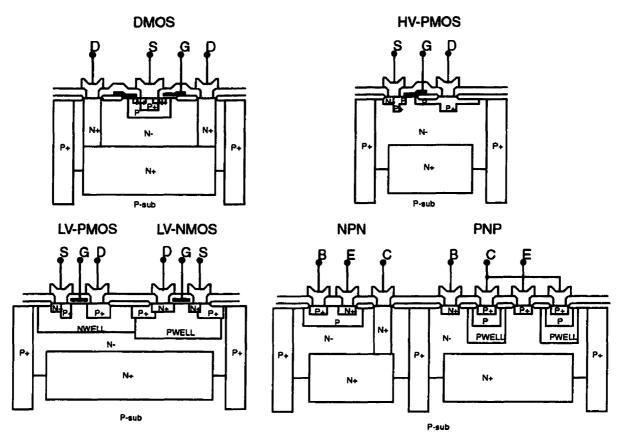

| Fig. 1.9: Cross-section of BCD process and compatible devices                     | 14         |

| Fig. 1.10: High voltage MOS devices in low voltage BiCMOS process                 | 15         |

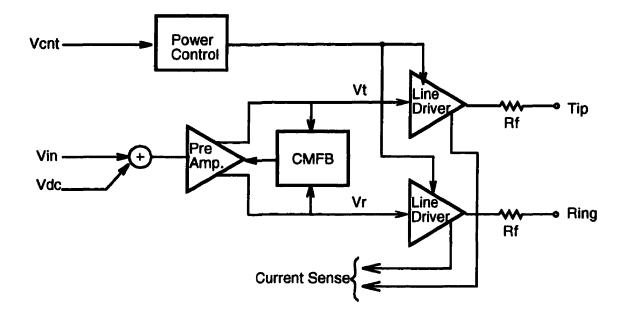

| Fig. 2.1: Architecture of the high voltage front-end of the short-loop SLIC       | 23         |

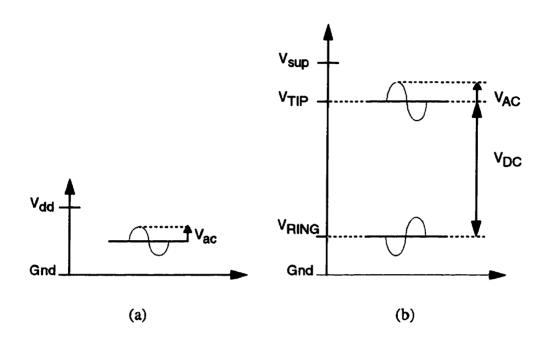

| ig. 2.2: Transmitting signal levels: a) low voltage signal from Codec b) loop sig | nal25      |

| ig. 2.3: A differential preamplifier structure                                    | 26         |

| ig. 2.4: Model of the CMFB loop                                                   | 27         |

| g. 2.5: Longitudinal balance model                                                | 29         |

| ig. 3.1: BATMOS-5 process flow                                                    | 34         |

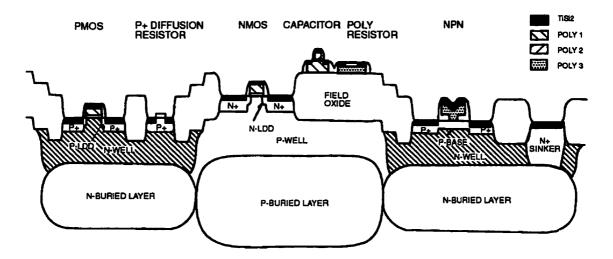

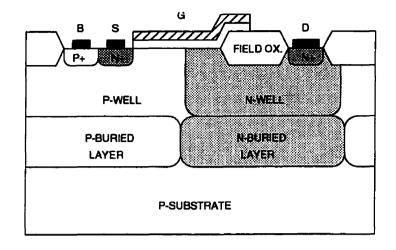

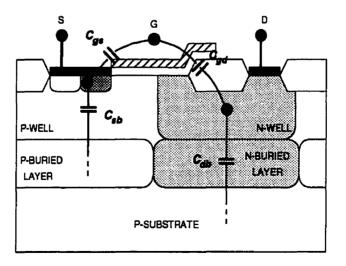

| g. 3.2: Cross section of the BiCMOS process [10]                                  | 35         |

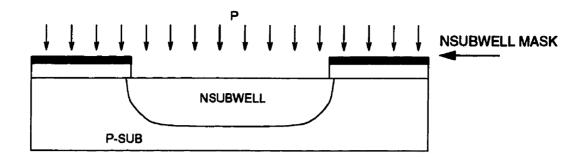

| ig. 3.3: NSUBWELL processing step                                                 | 37         |

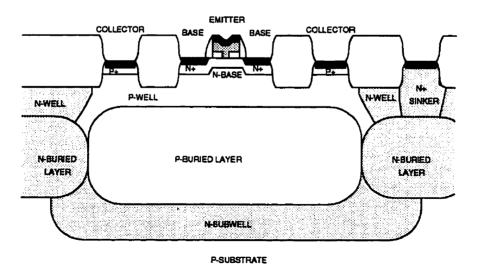

| ig. 3.4: Structure of PNP transistor in the 10V BiCMOS process                    | 37         |

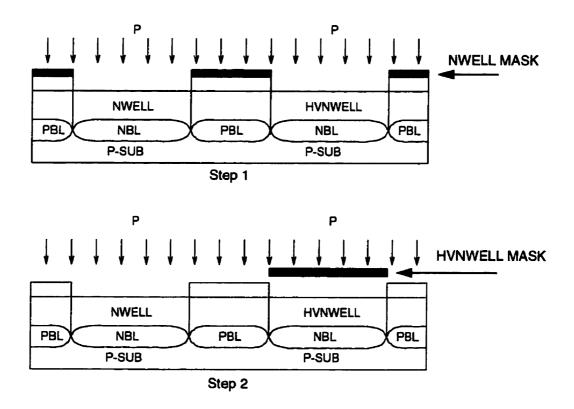

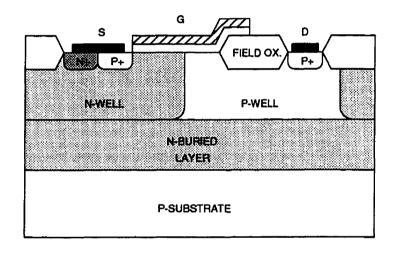

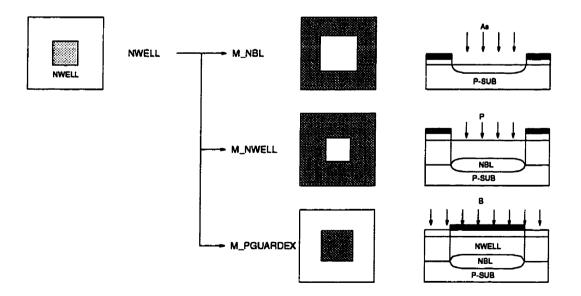

| ig. 3.5: Processing steps for implementing both n-well and HVn-well               | 38         |

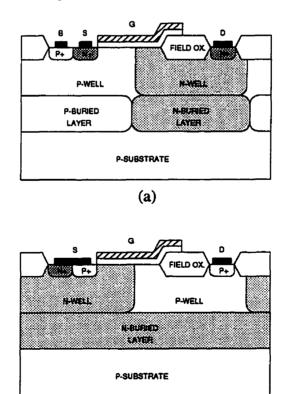

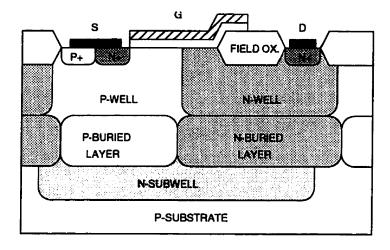

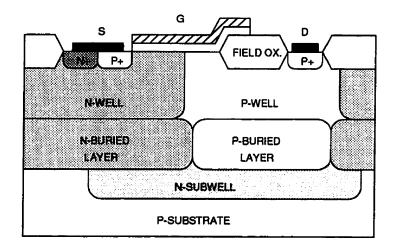

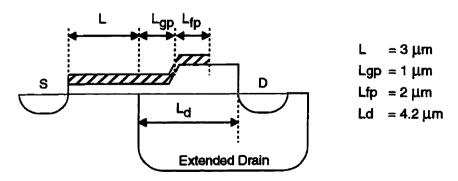

| ig. 3.6: Cross-section of: a) a high voltage NMOS and b) a high voltage PMOS      | in         |

| BATMOS-5                                                                          | 40         |

| ig. 3.7: Cross-section of: a) a high voltage NMOS and b) a high voltage PMOS i    | in         |

| BATMOS-10                                                                         | 41         |

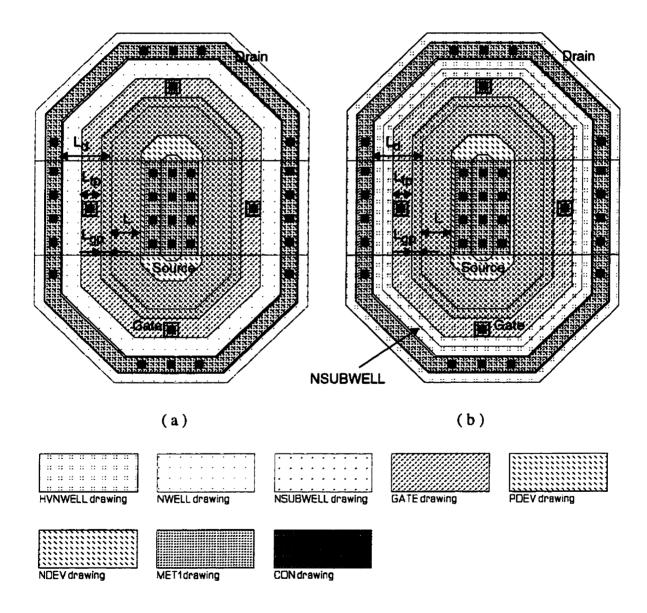

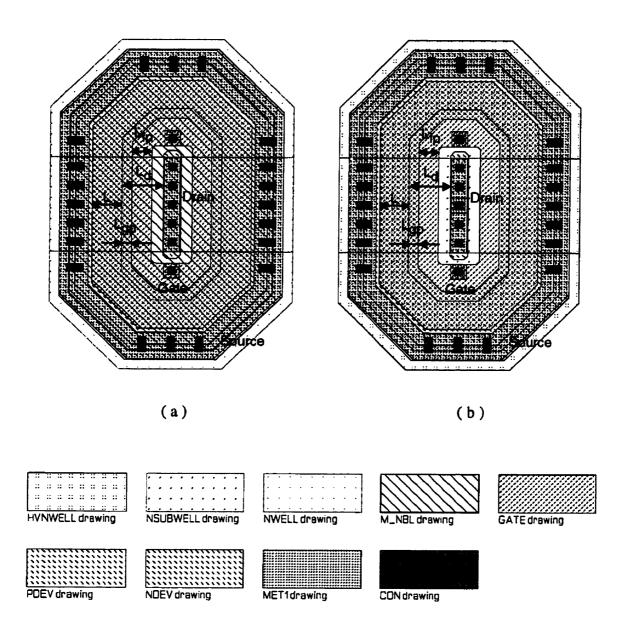

| ig. 3.8: Layouts of the high voltage transistors in BATMOS-5: a) NMOS and         |            |

| b) PMOS                                                                           | 42         |

| ig. 3.9: Micrographs of the high voltage transistors in BATMOS-5: a) NMOS an      | d          |

| b) PMOS                                                                           | 43         |

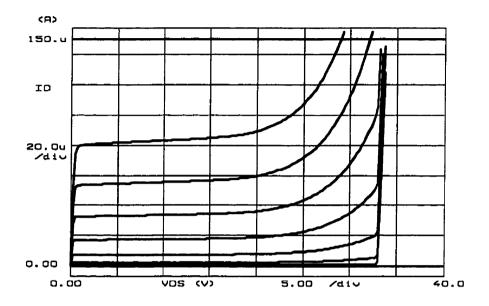

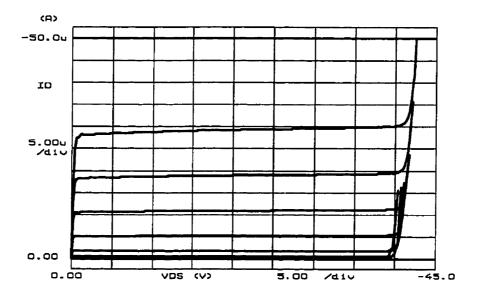

| Fig. 3.10: Measured I-V characteristics of the high voltage NMOS transistor in    |            |

| BATMOS-5 (W/L=10/3, Drift region length=4.2µm)                                    | 44         |

| Fig. 3.11: Measured I-V characteristics of the high voltage PMOS transistor in        |

|---------------------------------------------------------------------------------------|

| BATMOS-5 (W/L=10/3, Drift region length=4.2μm)45                                      |

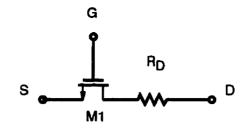

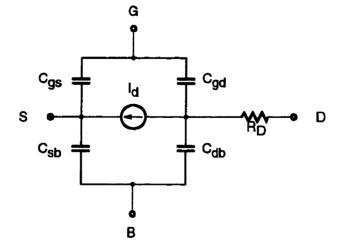

| Fig. 3.12: Circuit models for the extended-drain high voltage devices                 |

| Fig. 3.13: Simplified model structure used for parameter extraction                   |

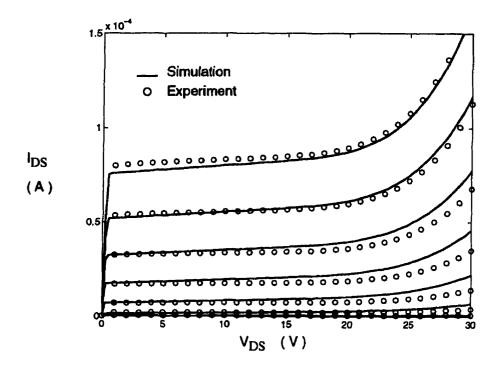

| Fig. 3.14: Experimental and simulated I-V characteristics of the high voltage NMOS in |

| BATMOS-5 (W/L=10/3, Drift region length= $4.2\mu m$ , $R_D=0.94k\Omega$ )48           |

| Fig. 3.15: Experimental and simulated I-V characteristics of the high voltage PMOS in |

| BATMOS-5 (W/L=10/3, Drift region length= $4.2\mu m$ , $R_D=12.4k\Omega$ )48           |

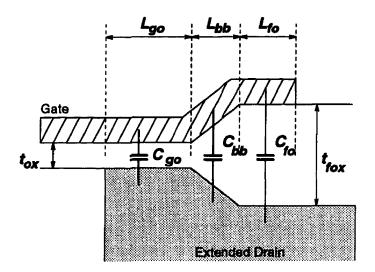

| Fig. 3.16: Modeling of the parasitic capacitances of the high voltage device          |

| Fig. 3.17: Model of the gate-drain capacitance of the high voltage device             |

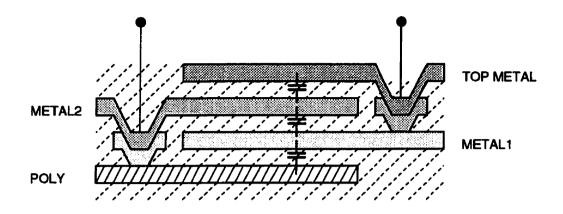

| Fig. 3.18: Structure of the high voltage capacitor                                    |

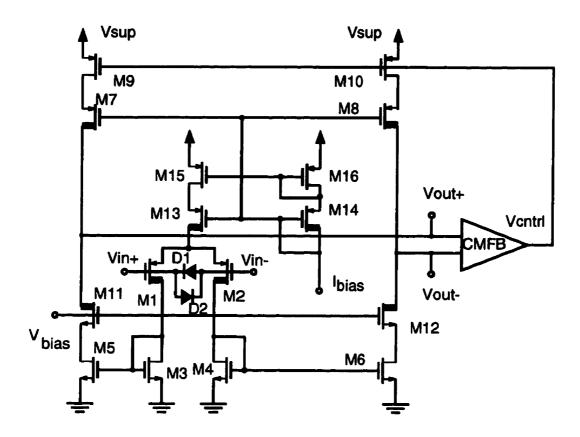

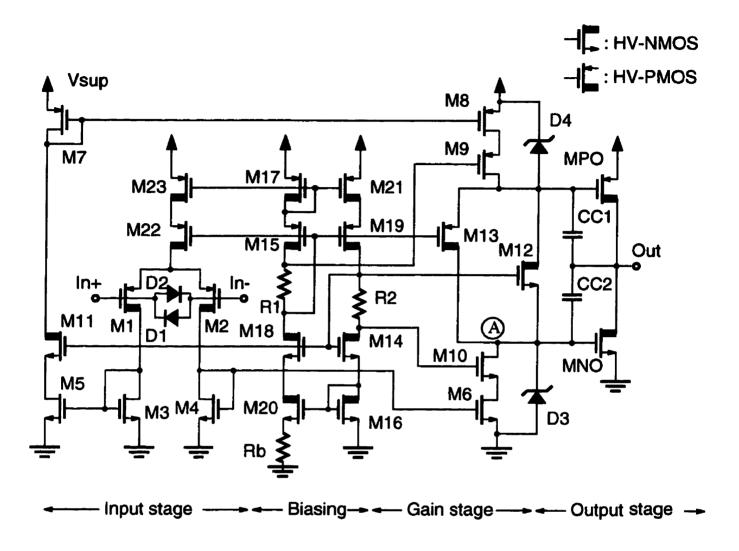

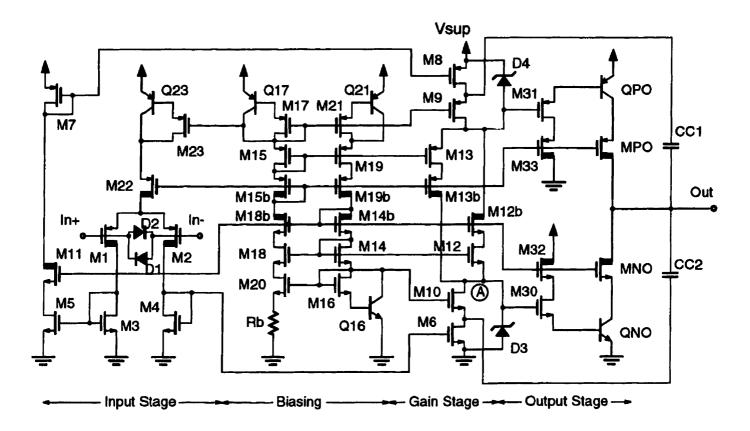

| Fig. 4.1: Schematic diagram of the differential opamp57                               |

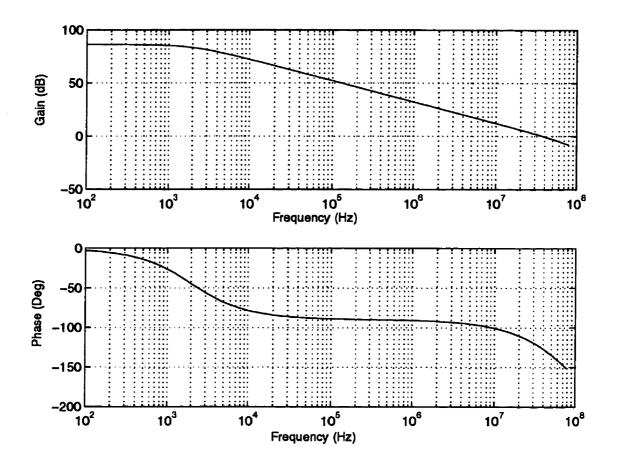

| Fig. 4.2: Frequency response of the differential opamp                                |

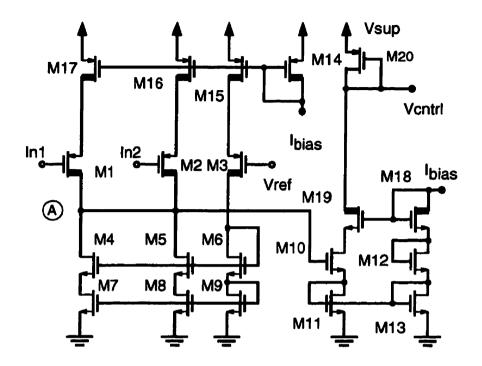

| Fig. 4.3: Schematic diagram of the common-mode feedback circuit60                     |

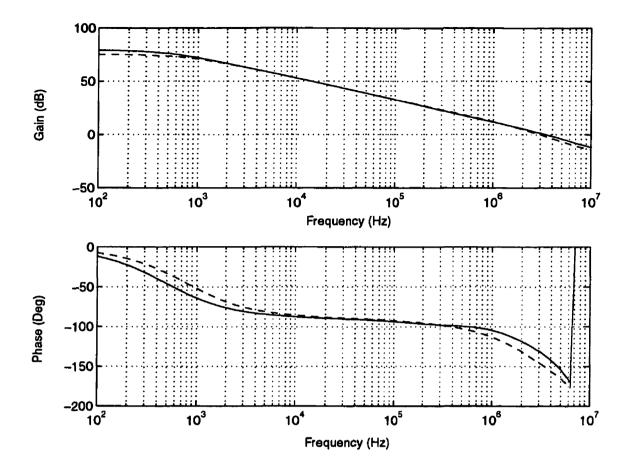

| Fig. 4.4: Frequency response of the CMFB loop61                                       |

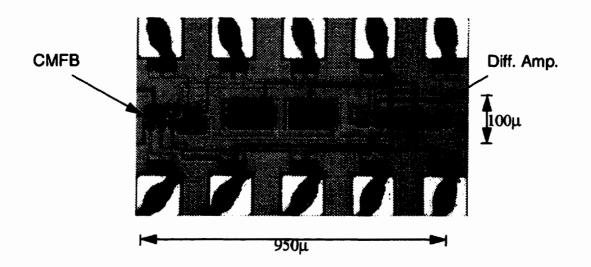

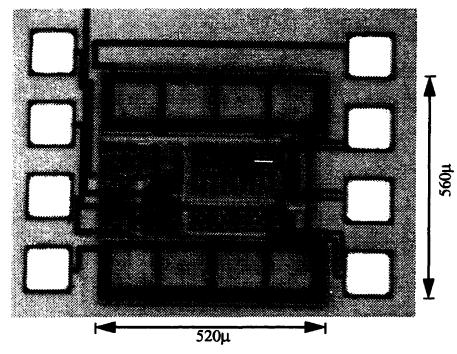

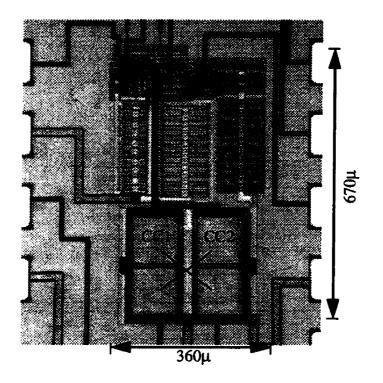

| Fig. 4.5: Micrograph of the differential opamp and the CMFB circuit                   |

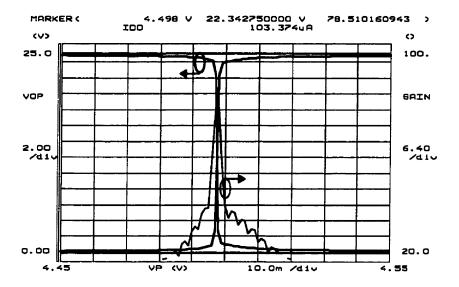

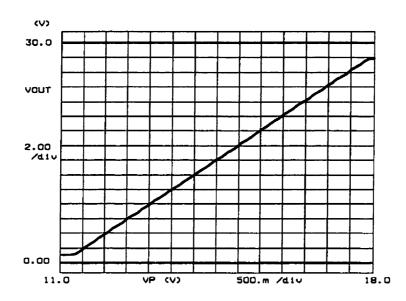

| Fig. 4.6: Transfer characteristics and gain of the differential opamp                 |

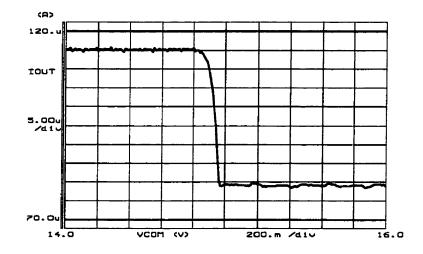

| Fig. 4.7: Transfer characteristics of the CMFB circuit63                              |

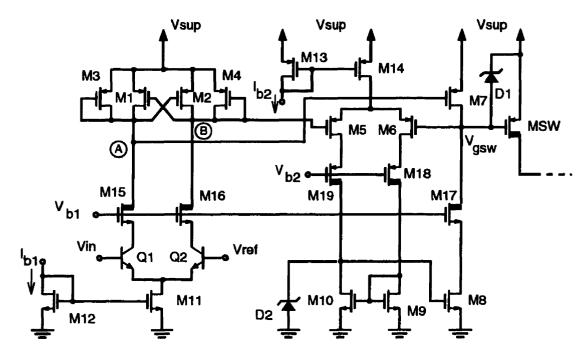

| Fig. 4.8: Schematic diagram of the power switch driver65                              |

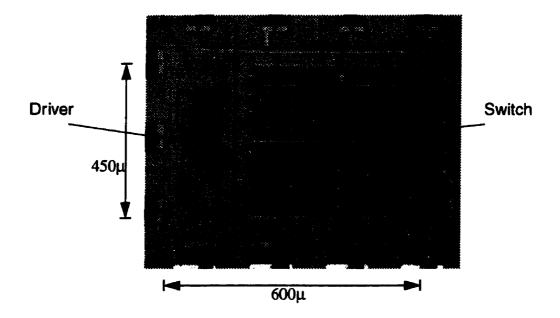

| Fig. 4.9: Micrograph of the power switch and the driver circuit                       |

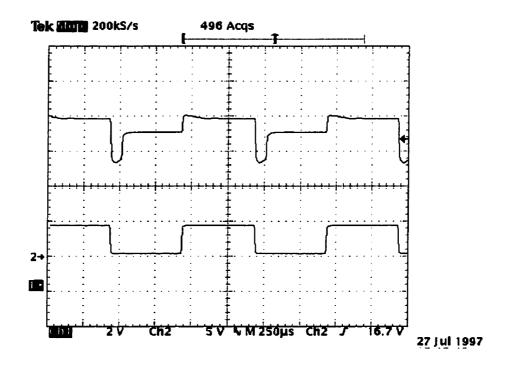

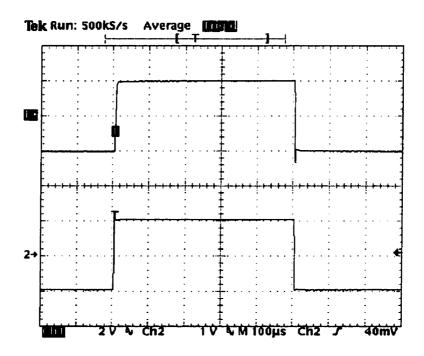

| Fig. 4.10: Waveforms of the switch driver circuit: Upper trace: Ch2-output,           |

| Lower trace: Ch1-input67                                                              |

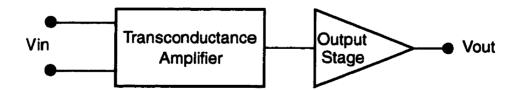

| Fig. 4.11: Architecture of a line driver                                              |

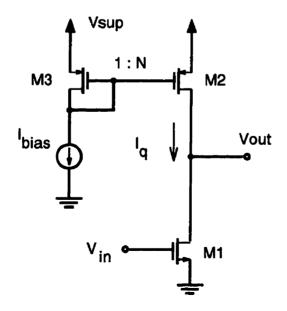

| Fig. 4.12: Class A output stage with current mirror biasing                           |

| Fig. 4.13: General structure of a class AB output stage70                             |

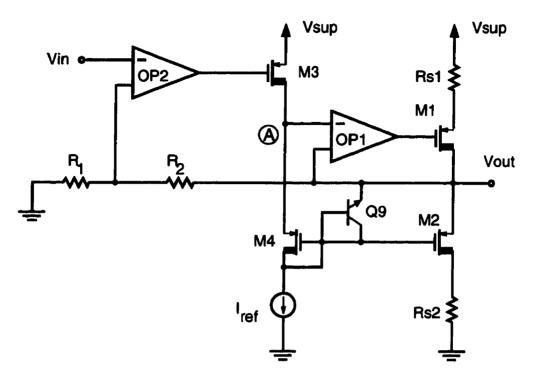

| Fig. 4.14: Schematic diagram of the CQCM line driver72                                |

| Fig. 4.15: Simplified diagram of the low-side CMOS quasi-current-mirror74             |

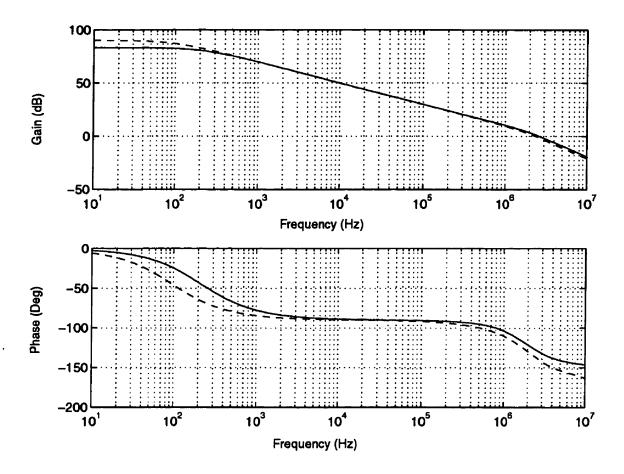

| Fig. 4.16: Frequency response of the compensated (CC1=CC2=4pF) CQCM line driver in    |

| current-sink (solid line) and current-source (dashed line) modes                      |

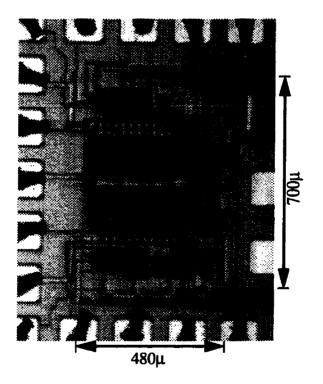

| Fig. 4.17: Micrograph of the line driver                                              |

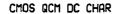

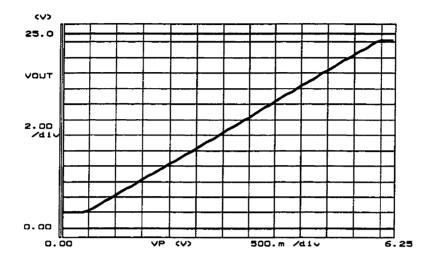

| Fig. 4.18: DC characteristic of the CQCM line driver                                  |

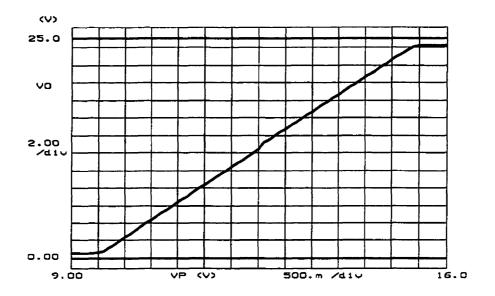

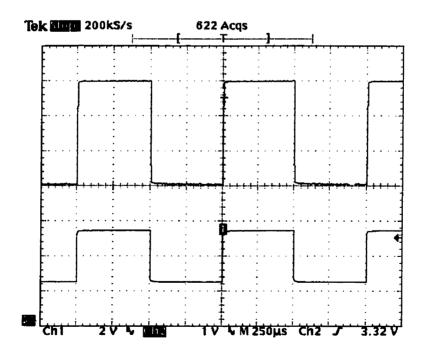

| Fig. 4.19: Step response of the CQCM line driver, Upper trace: Ch1-Output,                   |

|----------------------------------------------------------------------------------------------|

| Lower trace: Ch2-Input:81                                                                    |

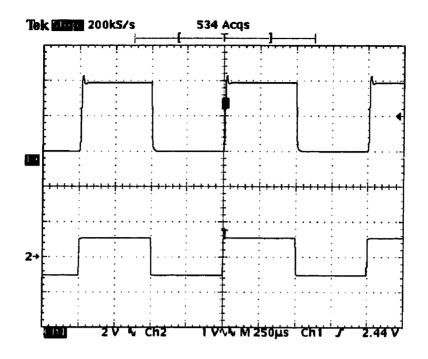

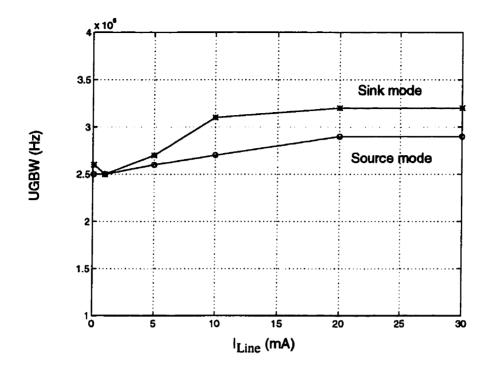

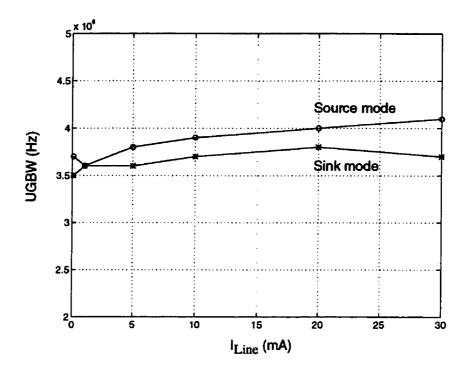

| Fig. 4.20: Unity-gain bandwidth (UGBW) of the line driver vs. the output current81           |

| Fig. 4.21: Schematic diagram of the BQCM line driver                                         |

| Fig. 4.22: Simplified diagram of the low-side BiCMOS quasi-current mirror stage86            |

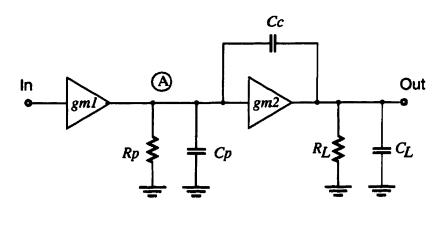

| Fig. 4.23: AC models for a) Miller, and b) cascode Miller compensation techniques89          |

| Fig. 4.24: Frequency response of the compensated (CC1=CC2=2pF) BQCM line                     |

| driver in current-sink (solid line) and current-source (dashed line) modes91                 |

| Fig. 4.25: Micrograph of the BQCM line driver                                                |

| Fig. 4.26: DC characteristic of the BQCM line driver with a gain of 4                        |

| Fig. 4.27: Step response of the BQCM line driver, Upper trace: Ch1-Output,                   |

| Lower trace: Ch2-Input93                                                                     |

| Fig. 4.28: Unity-gain bandwidth (UGBW) of the BQCM line driver vs. the output                |

| current                                                                                      |

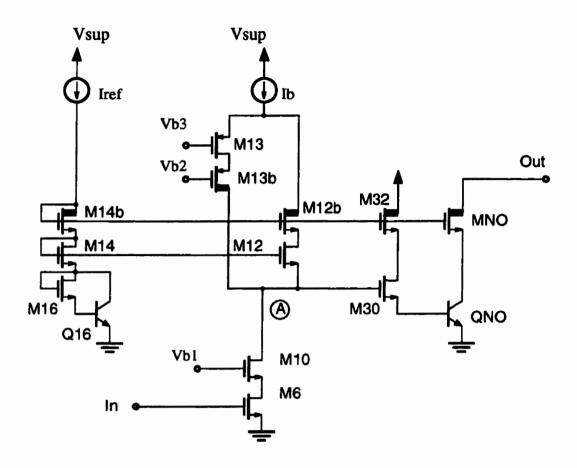

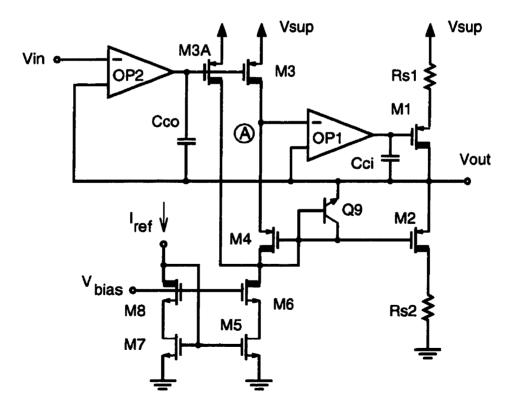

| Fig. 4.29: Schematic diagram of the FCM line driver                                          |

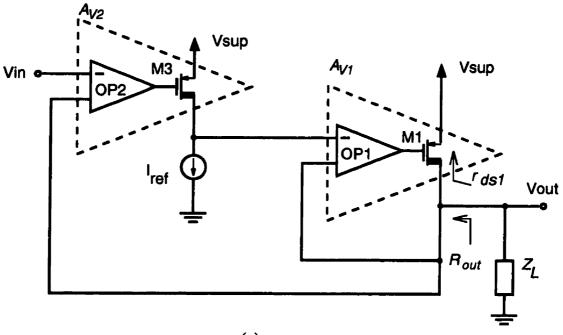

| Fig. 4.30: Simplified diagram of the FCM output stage                                        |

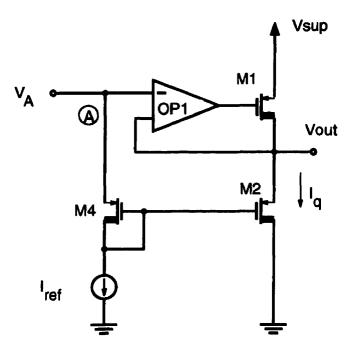

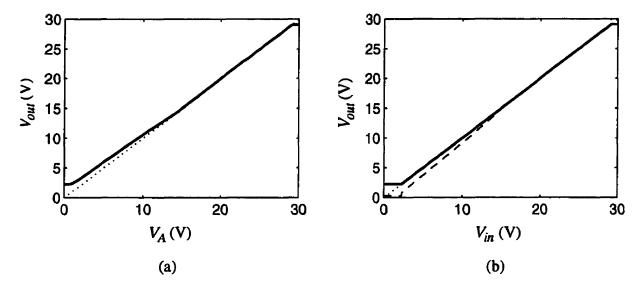

| Fig. 4.31: DC transfer characteristics of the FCM output stage: a) from $V_A$ to $V_{out}$ , |

| b) from V <sub>in</sub> to V <sub>out</sub>                                                  |

| Fig. 4.32: FCM output stage with a gain of more than one                                     |

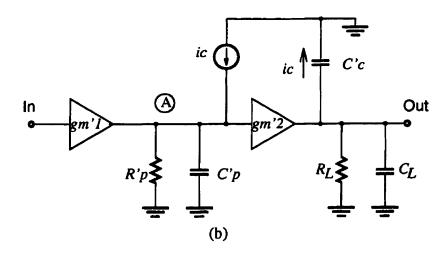

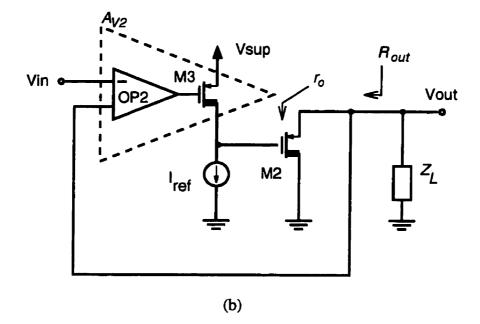

| Fig. 4.33: AC models for FCM output stage for a) pull-up and b) pull-down paths104           |

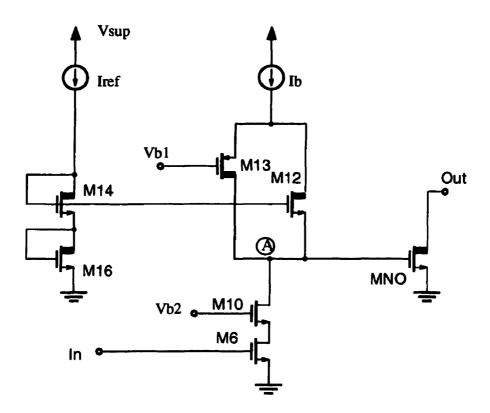

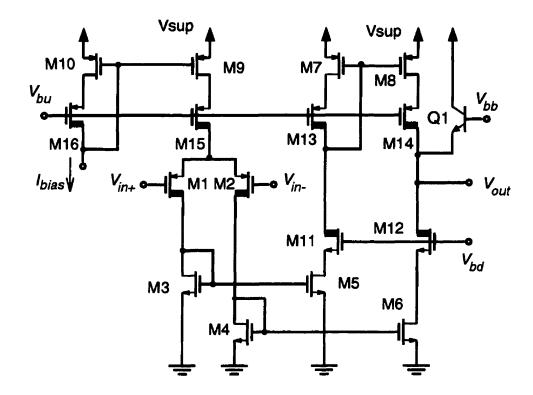

| Fig. 4.34: Schematic diagram of the internal opamps OP1 and OP2106                           |

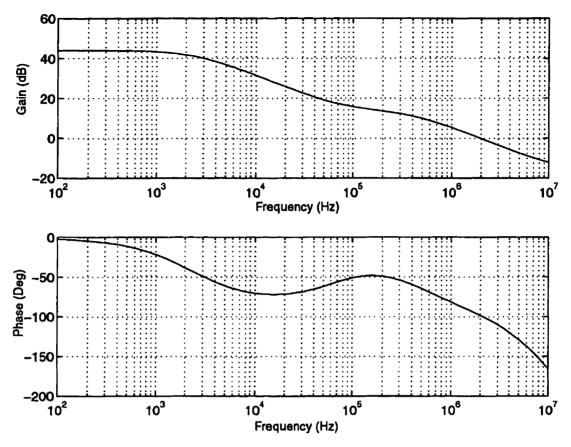

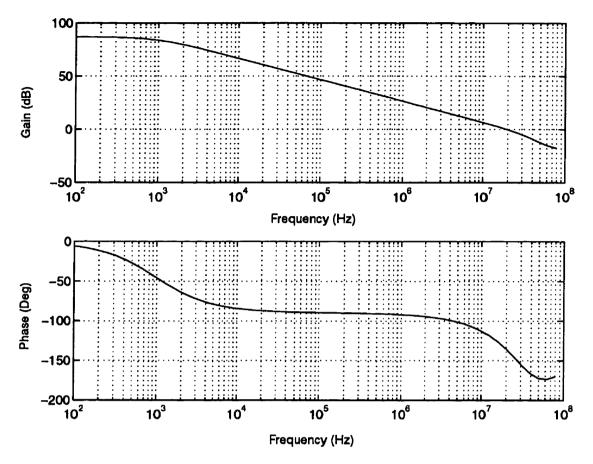

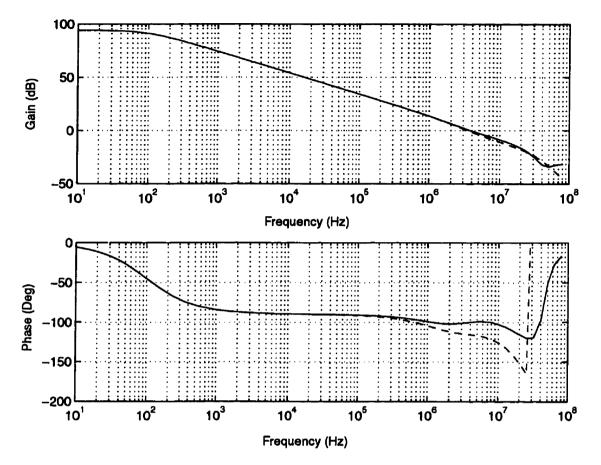

| Fig. 4.35: Frequency response of the internal opamps (Compensated with 3pF load              |

| capacitance)108                                                                              |

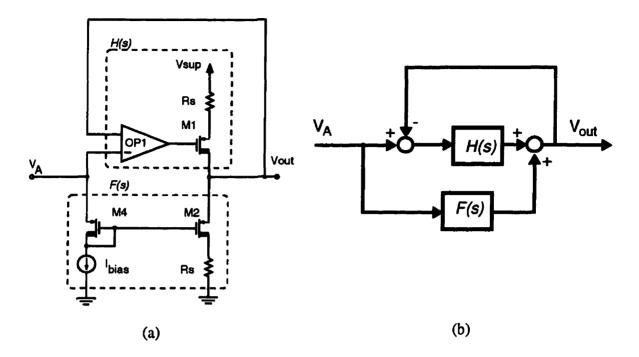

| Fig. 4.36: Inner feedback loop of the FCM output stage: a) AC signal paths and               |

| b) Block diagram109                                                                          |

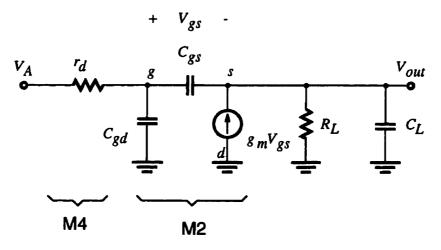

| Fig. 4.37: AC model of the feedforward path                                                  |

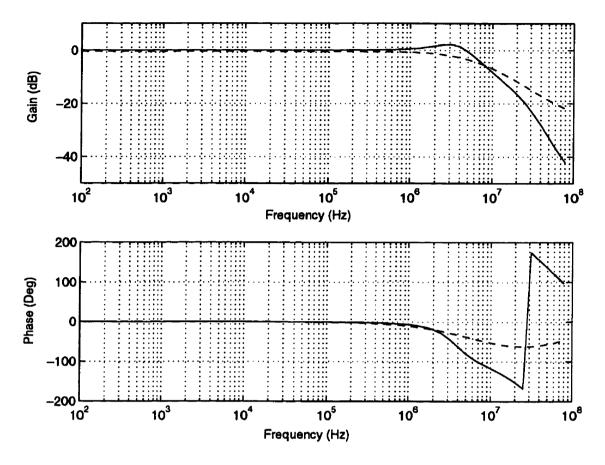

| Fig. 4.38: Frequency response of feedforward path F(s)                                       |

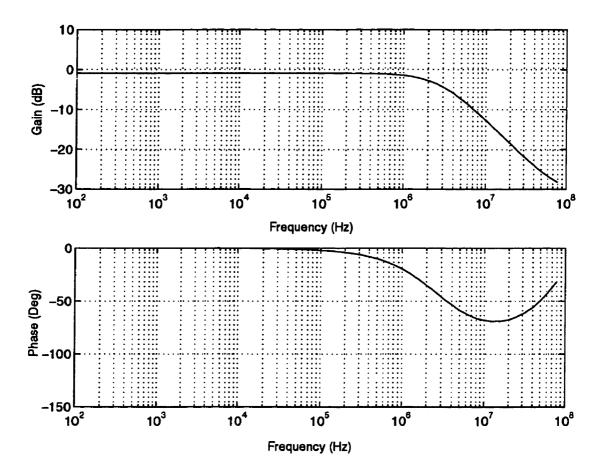

| Fig. 4.39: Frequency response of the output stage from $V_A$ to $V_{out}$ with feedforward   |

| (solid line) and without feedforward path (dashed line)                                      |

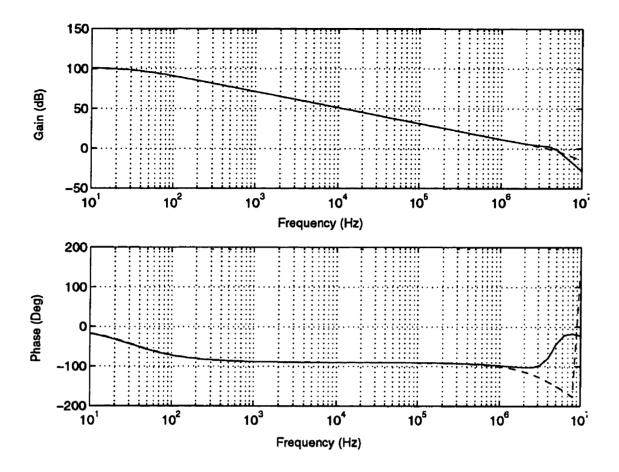

| Fig. 4.40: Frequency response of the inner feedback loop with a unity-gain feedback114       |

| Fig. 4.41: AC model for compensating the outer feedback loop                                 |

# Page

| 5 |

|---|

|   |

| 6 |

| 7 |

| 7 |

| 8 |

| 8 |

|   |

| 9 |

|   |

| 0 |

| 1 |

| 2 |

|   |

|   |

| 3 |

|   |

# List of Tables

| Table 2.1: Maximum loop resistance for different systems | 21  |

|----------------------------------------------------------|-----|

| Table 2.2: Major line driver specifications              |     |

| Table 3.1: Available devices in the 0.8µm BiCMOS         |     |

| Table 4.1: Device parameters of the differential opamp   | 57  |

| Table 4.2: Device parameters of the CMFB circuit         | 60  |

| Table 4.3: Preamplifier characteristics                  | 64  |

| Table 4.4: Device parameters of the power switch driver  | 65  |

| Table 4.5: Device parameters of the CQCM line driver     | 77  |

| Table 4.6: CQCM line driver characteristics              | 83  |

| Table 4.7: Device parameters of the BQCM line driver     |     |

| Table 4.8: BQCM line driver characteristics              |     |

| Table 4.9: Device parameters of the FCM line driver      | 102 |

| Table 4.10: Device parameters of the internal opamps     | 106 |

| Table 4.11: FCM line driver characteristics              | 119 |

# **CHAPTER 1**

## Introduction

The expanding demand for advanced subscriber services such as interactive internet access, multimedia and video-on-demand, is driving the current trend in the telecommunication industry towards providing efficient, broadband and low-cost local access networks. Currently, the widespread plain old telephone service (POTS), is the most cost-effective telecommunication infrastructure for providing multi-service access to residential and small business users. Over the past two decades, broadband technologies have been widely used in long distance and inter office transmission systems, increasing the capacity of the network as well as its quality and reliability. The old analog transmission system has evolved into a totally digital pulse-code-modulation (PCM) system with optical fibre and satellite links as the high capacity media. However, still after almost 100 years, the final connection from the central office to the subscriber has remained an analog twistedpair copper loop, limiting the data transmission rate.

The long survival of POTS is not due to the lack of a modern alternative technology. In fact, optical fibers have traditionally been used in the network core for many years because of their high capacity and long range capabilities. Rather, it is because the local exchange network involves a unique combination of cost and engineering barriers. With more than 600 million telephone subscriber worldwide, the investment required to replace the existing infrastructure is immense, while the investment return from domestic customers is limited.

Therefore broadband media such as optical fibers, although economical for long-distance high-volume transmission, are still far from replacing the copper lines.

In order to reduce the cost per customer in the new emerging technologies such as fiber-in-the-loop (FITL) or hybrid-fiber-coax (HFC), the broadband media are shared by a number of subscribers. In these techniques, broadband links extend beyond the central telephone office to a service access point close to the subscriber premises and short copper lines connect the subscriber to the service access point. The main advantages offered by these systems include:

- dividing the installation cost of the broadband system among many users, thus reducing the access cost per customer,

- reducing loop lengths to increase the maximum data transfer rate of the copper loops, and

- maintaining POTS compatibility (which is the main concern of the telephone companies).

In order to provide a variety of different services including voice, video and data, these new systems will require a large amount of VLSI circuitry. One of the most challenging blocks required is the subscriber loop interface circuit (SLIC) which provides the appropriate signaling for POTS. Conventional SLICs have long been used in telephone central offices to drive twisted pair copper loops. Traditionally, SLICs are implemented using a number of separate chips and discrete components to perform the various high voltage and low voltage functions required. Due to the high voltage requirements and functional complexity involved, the integration of SLICs has been an enduring challenge. Although dedicated high voltage integrated circuit processes have been used in implementing central office SLICs, the next generation of SLICs for shorter loops, will require a higher level of integration at much lower cost. This can best be achieved by using an advanced VLSI process with enhanced high voltage capabilities.

In the following sections, the conventional SLIC is introduced and its high voltage functions are discussed. The evolution of short loops and their application in future local access networks are then discussed followed by a review of the characteristics of short loop SLICs. The choice of an appropriate technology for short loop SLIC implementation is addressed next by considering the current state of high voltage integrated circuit processes and discussing new techniques used to increase the high voltage capabilities of a low voltage VLSI process. Finally, previous related work is reviewed and the objectives and outline of the thesis are presented.

## 1.1 Subscriber Loop Interface Circuits (SLIC)

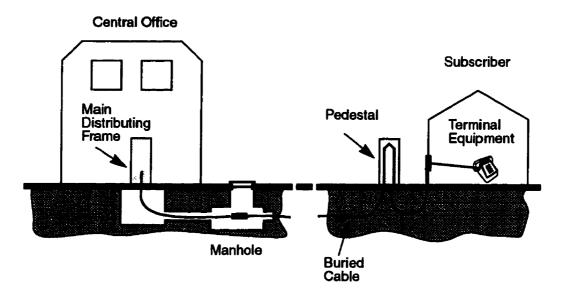

The subscriber loop refers to the circuit formed by twisted-pair copper lines (named Tip and Ring) connected to the central office or a private branch exchange (PBX) at one end and the terminal equipment (such as the telephone, fax machine,...) at the other end as illustrated in Fig. 1.1. Generally, the loop performs the following functions:

- provides power for the terminal equipment from the central office,

- transmits bidirectional voice or data signals between the calling and called parties,

- carries bidirectional control signals (supervision) between the subscriber and the central office, and

- passes ring signals to the called party.

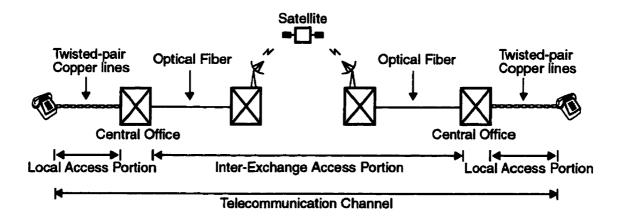

The subscriber loop can be considered as the exchange access portion of a telecommunication channel as illustrated in Fig. 1.2. The core of the transmission network between the central offices, referred to as the inter-exchange access, uses broadband communication channels such as optical fiber, microwave radio systems and satellite links

Fig. 1.1: Subscriber loop connecting the subscriber to the central office

incorporating digital PCM systems. The copper loops, as the end links of the communication channel, have remained completely analog as originally introduced.

The copper lines are connected to the line cards at the central office. For each subscriber, there is a subscriber loop interface circuit (SLIC) on the line card handling all the signaling through the loop. SLICs act as the interface between the digital PCM network and the analog loops.

Fig. 1.2: A typical telecommunication channel

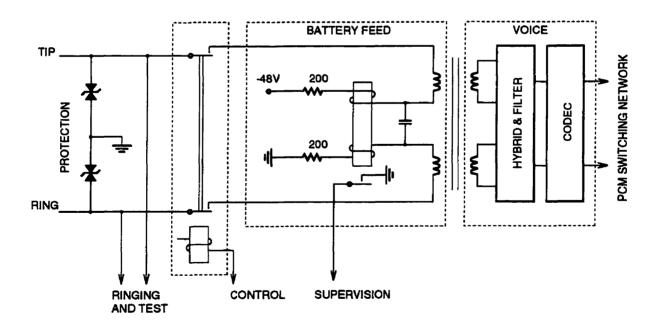

A SLIC must support a wide variety of functions referred to as BORSCHT functions [1-2]. BORSCHT stands for Battery feed, Overvoltage protection, Ringing, Supervision, Coding, Hybrid and Test. Fig. 1.3 shows a simplified diagram for a conventional SLIC, performing all of the above mentioned functions.

One of the main functions of the SLIC is to supply direct current from the central office battery to the loop. This is the only source of power for passive terminal equipment such as a telephone set. As shown in Fig. 1.3, the 48V DC source is connected to the loop through two 200 $\Omega$  feed resistors. The reason for the high battery voltage and the feed resistors is that the loop resistance changes over a wide range from almost zero for short loops, to 1500 $\Omega$ for long loops. While minimum power must be delivered to the telephone set in a long loop, the line current must be limited in a short loop with small resistance.

The SLIC is responsible for transmitting and receiving voice signals on the loop. The transmission on the loop is a full-duplex two-wire transmission while there are separate

Fig. 1.3: Schematic of a central office SLIC

channels for receiving and transmitting signals (four-wire) in the switching network. The hybrid circuit in the SLIC performs the two-wire to four-wire conversion. This circuit is connected to the PCM highway through a codec block including A/D and D/A converters. The SLIC must also provide a suitable ac impedance (ranging from  $135\Omega$  to  $1200\Omega$  for different standards) for a matched loop termination.

The loop current is monitored by the SLIC to determine the on-hook and off-hook conditions. Furthermore, all other signaling such as dialing, call processing tones and test signals are provided by the SLIC.

In order to ring the telephone set, a high voltage (90Vrms) ring signal is applied to the loop. The ringing signal frequency is in the range of 16 to 66 Hz. A ring signal generator on the line card provides the required signal which is switched to the loop by the SLIC.

Buried or aerial loop wires are exposed to hazardous electrical interference that may cause high potential surges in the loop. High voltage spikes caused by lightning, power lines contacts or power line induction can damage the circuits connected to the loop. Therefore, protection devices must be provided at both ends of the loop (at the central office and subscriber's premises) to prevent destructive damage.

## **1.2 Short Loops and Their Applications**

The current trend in the telecommunication industry is towards providing advanced subscriber services such as interactive internet access, video-on-demand and HDTV by deploying broadband communication systems into the existing telephone networks. However, the small bandwidth and poor noise and interference characteristics of twisted-pair copper loops severely limit their use for high-speed digital services.

The ideal solution is to replace the copper lines with a wideband media such as coaxial cables, optical fibers or radio links. This has led to a number of new proposed network

architectures such as fiber-in-the-loop(FITL)[3], hybrid-fiber-coax(HFC) [4] or wirelesslocal-loops (WLL) [5]. These systems are briefly described in the following sections.

#### 1.2.1 Fiber-In-The-Loop (FITL)

FITL refers to the use of fiber optic transmission beyond the central office and close to the subscriber. The ultimate goal of the telecommunication industry is to extend the fiber all the way from the central office to the terminal equipment at the subscriber's premises. This technology, referred to as fiber-to-the-home (FTTH), provides the full fiber bandwidth which offers enormous capacity to the user. However, replacing the whole copper infrastructure with a completely new system will not be economically feasible for the telephone industry for at least another decade [3].

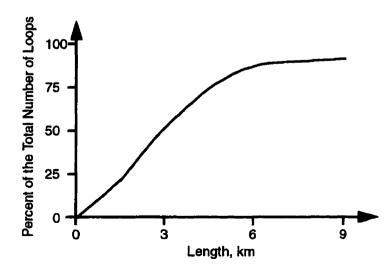

A loop survey compiled by Bellcore [6], shows that the average existing loop length is 3.5 km with more than 75% of the loops shorter than 4.5 km. Fig. 1.4 shows the loop length distribution in residential areas [6]. While fiber connections are more economical for loops longer than 4 km (which mostly use digital loop carriers such as T1), they are too costly for a majority of loops with lengths shorter than 4 km [6].

Fig. 1.4: Cumulative distribution of existing loops in terms of length [6]

A rough estimate for the first installation cost of a FTTH system is about \$1500 per customer [3]. Therefore, replacing the entire copper network would require a huge investment in the range of trillions of dollars. Any payoff from such a large investment must come from the customer who is not expected to require the extremely wide bandwidth of the whole fiber in near future.

Furthermore, replacing the existing infrastructure would take no less than two decades. The fastest estimated rate of installing new cables is 7% per year [7]. Since the number of telephone lines is growing at about 3% annually, the net replacement rate would only be 4%.

Studies [7] conclude that the transition from copper to fiber is not likely to happen in one step. Therefore, the telephone companies are looking for interim solutions towards the broadband network of the future. One of the most popular solutions is fiber-to-the curb (FTTC) which is capable of supporting POTS and can eventually be upgraded to FTTH [8].

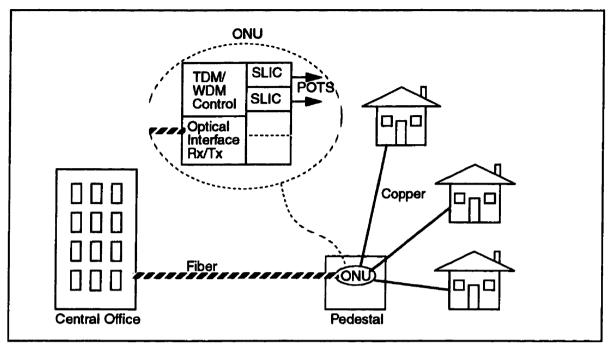

In FTTC systems, fiber is brought to within 150-300m of the subscriber to an optical network unit (ONU) located on a pedestal<sup>1</sup>. Copper drops then carry the POTS signals from the ONU to the subscriber. Fig. 1.5 illustrates a FTTC architecture. In the ONU, there is an optical interface for transmitting and receiving signals over the fiber. The ONU also includes circuitry for multiplexing and demultiplexing different signals onto the optical channel. Both time division multiplexing (TDM) and wavelength division multiplexing (WDM) are used in the proposed systems. SLICs are also included in the ONU to drive the short copper loops.

The intent of the FTTC system is to share the cost of the optical network among many subscribers. The level of sharing represents a trade-off between cost and bandwidth. If a

<sup>1.</sup> FTTC systems are also called Fiber-To-The-Pedestal (FTTP)

Fig. 1.5: Schematic of a fiber-to-the-curb system

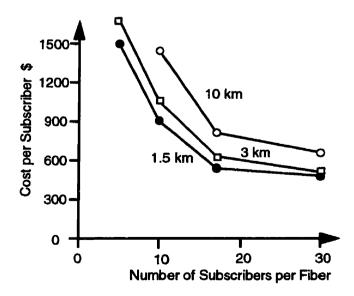

large number of customers are served by the ONU, the cost of common functions on a perline basis can be reduced. On the other hand, moving the fiber further away from the customer increases the copper length reducing the data transfer rate. Fig. 1.6 shows an estimate for the cost per subscriber versus the number of customers sharing the same fiber [9].

Fig. 1.6: Estimated initial cost of the installation of FTTC systems per customer

#### **1.2.2 Hybrid-Fiber-Coax (HFC)**

Although the fiber bandwidth is shared by a number of customers, the capacity of FTTC is expected to be sufficient for the near future. Short loops in the range of 100 meters are capable of transmitting in excess of 10Mbit/s, while placing shielded pairs in the loop could provide transmission rates of up to 100 Mbit/s. A coaxial cable could broadcast as many as 150 NTSC video channels or multiple DS-3 (45 Mbit/s) signals. Such bandwidths can be achieved with hybrid-fiber-coax (HFC) systems [6].

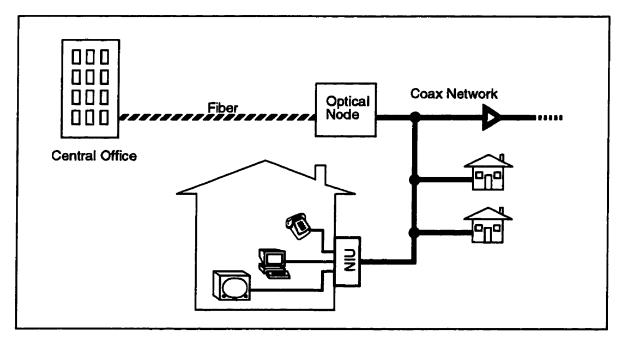

The HFC mostly supported by cable TV companies, is mainly designed for providing interactive multimedia services such as video-on-demand [4]. However, they are also capable of supporting POTS and data. Fig. 1.7 illustrates the structure of a HFC system. The central office transmits optical signals over the fiber to an optical node installed in the serving area. Optical signals are then converted to electrical ones at the optical node and are transmitted to the subscribers through a coaxial cable network typically serving a couple hundred users. A network interface unit (NIU) installed in a wall-mounted box at the

Fig. 1.7: Schematic of a hybrid-fiber-coax system

subscriber's home, separates different services for computers, TVs and telephone sets. To drive telephone lines inside the house there will be a SLIC in the wall box as well as other interface circuits for other services.

#### **1.2.3 Wireless Local Loops (WLL)**

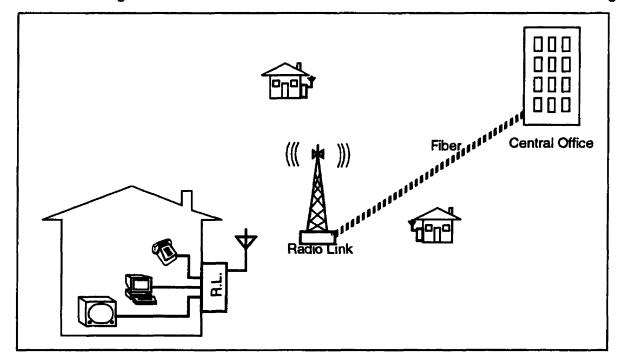

Wireless Local Loop (WLL) is a generic term for a local access system in which a wireless link instead of conventional copper lines, is used to connect subscribers to the local exchange office. Originally, WLL systems were proposed as a cost effective solution to provide voice service for developing nations without a widespread wired telecommunication network. A large portion of the total investment and the development time in providing telephone access in rural areas is spent on installing subscriber loops. By using a wireless link, the telephone network can penetrate far into the unwired areas in a short period of time because of the small amount of construction involved in installing a WLL system. A typical WLL architecture is illustrated in Fig. 1.8. The central office is connected through a fiber or coax cable to a radio link which can be installed on a building

Fig. 1.8: Schematic of a wireless local loop system

or a utility pole in a residential area. A wall-mounted box at the subscriber's house includes a radio transceiver as well as short loop SLICs and other interfaces for telephone sets and data terminals.

Recently, WLL has gained increased attention in the developed and underdeveloped countries as a potential rival to other broadband access architectures. Using existing cellular and PCS infrastructures, WLL can deliver voice and data services at higher rates and lower cost [5].

## 1.3 High Voltage Integrated Circuits Processes

The implementation of SLICs requires the use of high voltage integrated circuits (HVIC) which are defined as integrated circuits that combine high voltage devices with low voltage components on a single chip. Using mostly lateral devices, HVICs are able to sustain high voltages with limited current handling capability.

High voltage integrated circuits are usually classified in terms of the type of isolation technique employed [10]. The three types of isolation schemes encountered are: junction isolation (as in bipolar processes), self isolation (as in CMOS) and dielectric isolation including silicon-on-insulator (SOI) processes. Although SOI technologies provide superior performance, they are not attractive due to their high complexity and cost. Therefore, most practical HVIC solutions are based on junction or self isolated processes.

There are two major approaches to developing junction isolated or self isolated technologies for HVICs. In one approach, an optimized high voltage device structure is designed and the low voltage control components are built around it. This results in high performance high voltage devices but poor-quality low voltage components. The other approach involves starting with a low voltage CMOS or BiCMOS process and incorporating high voltage devices within it. Since these processes are not optimized for high voltage operation, the performance of the high voltage components is usually limited.

A dedicated HVIC process, based on the former approach, usually uses a thick epitaxial layer (10 to  $25\mu$ m) to provide high breakdown voltages. However, the controllability of such processes is more complicated as a result of deep diffusions required. Also, a larger isolation area, larger feature sizes and increased parasitics, severely degrade the performance of the low voltage devices. Therefore, compared to a low voltage VLSI process, dedicated HVIC technologies provide less integration density at a much higher cost.

Prior to the mid-eighties, most high voltage ICs were realized using pure bipolar processes. With the growing request to incorporate more control logic functions on the chip, CMOS replaced  $I^2L$  logic in the control sections of high voltage ICs. Meanwhile, the advent of power MOS devices which unlike bipolars, do not need DC driving current and provide fast switching speed, greatly influenced the development of high voltage ICs. Advanced high voltage IC processes merge different device structures onto the same chip. Junction isolated BCD (Bipolar, CMOS DMOS) smart power technology[11] is an example of such a process, a cross section of which is illustrated in Fig. 1.9. BCD processes were first introduced in the late eighties. The main high voltage devices are vertical n-channel DMOS transistors and extended drain PMOS devices. The process also provides low voltage CMOS and bipolar transistors. The first generation of BCD processes offered 4µm minimum gate length DMOS devices in three different versions with voltage ratings of 60 V, 100 V and 250 V, respectively. The main difference between these three versions is the thickness of the epitaxial layer (10-23 $\mu$ m). In the second and third generations [12], the minimum feature size was reduced to 2.5µm and 1.2µm respectively, with the latest submicron version providing 0.6µm DMOS transistors with 0.8µm, low voltage CMOS devices. However, the breakdown voltage has drastically dropped from 250V to 16 to 40V for lateral devices and 60 to 80 for DMOS transistors. Also with more than 20 masks, the complexity and cost of this process is much higher than a low voltage BiCMOS technology.

Fig. 1.9: Cross-section of BCD process and compatible devices

On the other hand, adding high voltage capabilities to a low voltage process can be advantageous in applications where low voltage circuits form a large proportion of the system. This approach is more economical as the cost of an advanced low voltage CMOS or BiCMOS process is much lower than that of a BCD type technology. Moreover, because of the higher levels of integration, this approach results in further area and cost reduction for complex systems. The ability of using existing low voltage circuit libraries also helps reduce the development time and cost.

Fig. 1.10 shows the cross section of high voltage NMOS and PMOS devices compatible with a submicron BiCMOS process [13-14]. These structures are based on a lateral extended drift region at the drain of the transistor to withstand high voltages. In order to keep the compatibility with the low voltage process and avoid additional processing steps, the low doped well regions are used as the drain drift region. These devices are

implemented by appropriate layout without any modification to the low voltage process. Further improvements to the lateral devices can be achieved by utilizing the reduced surface field (RESURF) concept in the design [15].

#### 1.4 Previous work on SLICs

The challenge of integrating SLICs stems from the variety of different functions and the wide range of operating voltages and power required. There have been various attempts at developing central office SLICs using dedicated HVIC processes. Due to limited density and flexibility of these processes, these chips can only include a small number of the SLIC functions. As a result, today's line cards include a chip set along with a number of off-chip components such as transformers, relays and other discrete devices. Although this thesis is the first work that specifically targets the integration of a short loop SLIC in a low voltage process, it is useful to review reported solutions for conventional SLICs.

Fig. 1.10: High voltage MOS devices in low voltage BiCMOS process

**(b)**

Several attempts at integrating SLICs in a dielectrically-isolated bipolar process have been reported [16,17]. However, they have remained at the experimental stage without offering a real practical solution as a result of their high cost.

Until recently, when the BCD (Bipolar-CMOS-DMOS) technologies became popular [18,19], most of the proposed SLICs were implemented in high voltage bipolar processes [20]. As a result, they included only a limited amount of control circuitry, usually implemented in  $I^2L$  logic. Consequently, a multi-chip approach was used to separate the low voltage and high voltage functions [21-22]. Currently, there exist a number of commercial ICs for SLIC applications implemented using high voltage bipolar processes. The latest line of products in this category allows the use two different power supplies to compensate for the loop length variations [23].

Recent attempts at implementing monolithic SLICs, include the implementation of high voltage amplifiers for line driving functions, fabricated in a 100V version of the BCD process[24]. These amplifiers, designed for conventional SLICs use a combination of class AB and class B output stages to control the quiescent current and provide high output current. These circuits mostly use vertical DMOS and high voltage PMOS devices to withstand the high operating voltages. Although these circuits can be useful for conventional SLICs, they are not suitable for short loop applications due to their large area  $(4 \text{ mm}^2 \text{ for each line driver})$  and limited bandwidth (less than 1MHz).

Another multi-chip solution for a SLIC has been reported recently [25]. This chip was implemented in a 170V BCD process [18]. It occupies 30 mm<sup>2</sup> of area and dissipates 1.3 W. Similar to other HVIC SLICs presently available, this SLIC also suffers from limited density and high cost.

Because all the available SLICs use a dedicated HVIC process, they are economically unattractive for short loop applications where a compact and low cost solution is desirable.

16

Therefore, it would be quite advantageous to consider a cost effective low voltage process for implementing a short loop SLIC. There has been no previous report of such an approach to solving the problem prior to the work presented in this thesis.

## **1.5** Objectives and Outline of the Thesis

Several architectures are presently competing to become the dominant local access network of the future. Although their characteristics and cost differ over a wide range, the need for short loop copper access is ubiquitous. The escalating capacity and complexity of the new systems require better performance and a higher level of integration at minimum cost. Yet, to maintain the compatibility with POTS, the high voltage requirements of the short loops must be satisfied. Thus, the objective of this thesis is to investigate the feasibility of integrating the high voltage building blocks of a short loop SLIC in an advanced low voltage submicron BiCMOS process. By enhancing the voltage handling capabilities of the BiCMOS process, the high voltage building blocks are designed and implemented with minimum area and power in order to efficiently integrate a large amount of low voltage circuitry on a single chip. Achieving this goal results in a highly economical solution for the cost-driven local access networks of the future.

In Chapter 2, the requirements for short loop system are discussed. An architecture for the SLIC's high voltage front-end is proposed and the high voltage building blocks are introduced. Chapter 3 deals with device and process issues. The high voltage capabilities of the BiCMOS process used in this thesis are examined in this chapter. The structures, layouts and mask layers used for implementing different high voltage devices are described and a set of electrical circuit models are developed.

Chapter 4 contains a detailed description of the SLIC components. The design of the high voltage building blocks are presented along with the implementation and experimental results. Conclusions and guidelines for future work are presented in Chapter 5.

17

### References

- [1] W. D. Reeve, Subscriber Loop Signaling and Transmission Handbook, Analog, IEEE Press, New York, 1992.

- [2] W. D. Gayler, *Telephone Voice Transmission*, Prentice-Hall, New Jersey, 1989.

- [3] C. J. Brunet, "Hybridizing the Local Loop," IEEE Spectrum, pp. 28-31, July 1994.

- [4] B. Kaplan, "Hybrid Fiber-Coax(HFC) Architecture Overview," The International Society for Optical Engineering Proceedings of the Hybrid Fiber-Coax Systems Conference, pp. 34-38, 1995.

- [5] A. Thryft, "Local Loops Take Wireless Routes," *Electronic Engineering Times*, pp. 96-97, March 1997.

- [6] W. K. Ritchie and J. R. Stern, *Telecommunications Local Networks*, Chapman & Hall, London, UK. 1993.

- [7] Alcatel, "Full Service Network Technology," http://www.alcatel.be/int2\_06.html.

- [8] C. P. Engineer, "Fiber In The Loop: An Evolution in Services and Systems," The International Society for Optical Engineering Proceedings of the Fiber Optics in the Subscriber Loop Conference, pp. 19-29, 1990.

- [9] J. R. Jones and R. B. Sharpe, "Cost Aspects of Narrowband and Broadband Passive Optical Networks," The International Society for Optical Engineering Proceedings of the Fiber Optics in the Subscriber Loop Conference, pp. 106-118, 1990.

- [10] B. Murari, F. Bertotti and G. A. Vignola, Smart Power ICs, Technologies and Applications, Springer, 1995.

- [11] A. Andreini, C. Contiero and P. Galbiati, "A New Integrated Silicon Gate Technology Combining Bipolar Linear, CMOS Logic and DMOS Power Parts," *IEEE Trans. Electron Devices*, vol. ED-33, pp. 2025-2030, 1986

- [12] B. Murari, "Smart Power Technology and The Evolution from Protective Umbrella to Complete System," *IEEE International Electron Device Meeting (IEDM)*, Dig. Tech. Papers, pp. 9-15, 1995.

- [13] R. Hadaway, P. Kempf, P. Schvan, M. Rowlandson, V. Ho, J. Kolk, B. Tait, D. Sutherland, G. Jolly, and I. Emesh, "A sub-micron BiCMOS technology for telecommunications", ESSDRC Proceedings, pp. 513-516, 1991.

- [14] Y. Q. Li, C.A.T. Salama, M. Seufert, P. Schvan and M. King, "Submicron BiCMOS compatible high-voltage MOS transistors," *Proceedings of the sixth International Sym*posium on Power Semiconductor Devices and ICs (ISPSD), pp. 355-359, 1994.

- [15] M. Liu, C.A.T. Salama, P. Schvan and M. King., "A Fully Resurfed, BiCMOS-Compatible High Voltage MOS transistor," Proceedings of the eight International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 143-146, 1996

- [16] R. M. Siri, P. J. Meza, D. P. Laude and R. C. Strawbrich, "Integrated Electronic Subscriber Line Interface Circuit with Ringing on Chip," *IEEE J. Solid-State Circuits*, vol. SC-18, pp. 665-667, 1983.

- [17] M. Akata, Y. Nagataki, K. Koyabu, K. Mukai, S. Yoshida, S. Morisaki, M. Eda, I. Ueki and T. Matsui, "A No-Trimming SLIC Two-Chip Set with Coin Telephone Signaling Facilities," *IEEE J. Solid-State Circuits*, vol. 25, pp. 458-465, 1990.

- [18] K. Wiesinger, W. Kanert, E. Glenz, N. Krischke, P. Nelle, H. Peri, F. Rfirsch, W. Schwetlick, C. Wagner and W. M. Werner, "SPT 170 A Smart Power Technology Combining Robust High-Voltage devices with Precision Analog Performance," *ISPSD Proceedings*, pp. 54-57, 1995.

- [19] A. Pariani and W. Rossi, "SLIC chip set adapts to different line lengths," *Electronic Engineering*, pp. 59-62, October 1990.

- [20] R. J. Apfel, K. E. Fields, J. C. Kuklewicz and Mark L. Stephens, "A Subscriber Line Interface Circuit with an Internal Switching Regulator," *International Solid-State Circuits Conference (ISSCC), Dig. Tech. Papers*, pp. 149-150, 1983.

- [21] R. K. Chen, T. H. Lerch, J. S. Radovsky and D. A. Spires, "A 90V Switching Regulator and Lightning Protector Chip Set," *International Solid-State Circuits Conference* (ISSCC), Dig. Tech. Papers, pp. 220-221, 1986.

- [22] A. Goodenough, "SLIC Ejects Relays From PABX Line Cards," *Electronic Design*, pp. 55-64, July 1994.

- [23] AM79R79 Ringing SLIC Data Sheet, Advanced Micro Devices, 1996.

- [24] R. Castello, F. Lari, M. Siligoni, and L. Tomasini, "100-V High-performance amplifiers in BCD technology for SLIC applications," *IEEE J. Solid-State Circuits*, vol. 27, pp. 1255-1263, 1992.

- [25] B. Zojer, R. Koban, R. Petschacher, W. Sereinig, "Integration of a Subscriber Line Interface Circuit (SLIC) in a New 170V Smart Power Technology," Proceedings of the Seventh International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 293-297, 1995

- [26] M. Aliahmad, C.A.T. Salama, "A 30V Line Driver in Submicron BiCMOS Technology," Proceedings of the eight International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 61-64, 1996

- [27] M. Aliahmad, C.A.T. Salama, "A Short Loop SLIC in a Submicron BiCMOS Technology," Proceedings of the ninth International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 329-332, 1997

- [28] M. Aliahmad, C.A.T. Salama, "A High Voltage Line Driver for Subscriber Loop Interfaces in a Low Voltage Submicron BiCMOS Technology," Accepted for publication in *Analog Integrated Circuits and Signal Processing Journal*, 1997.

- [29] M. Aliahmad, C.A.T. Salama, "Integration of a Short Loop SLIC in a Low Voltage Submicron BiCMOS Technology," Accepted for publication in *IEEE J. Solid-State Circuits*, 1997.

# CHAPTER 2 Short Loop SLIC System

### 2.1 Introduction

The challenge in integrating SLICs stems from the variety of different functions and the wide range of operating voltages and power which must be implemented on chip. While a large number of codec and control functions are required in the low voltage back-end of the system, line feed functions are the bottleneck at the high voltage front-end. A successful approach to such integration must include careful system design as well as suitable choice of technology. This chapter deals with the system aspects and the proposed architecture for the short loop SLIC. Technology issues and the characteristics of the process used to implement the system is the subject of the next chapter.

The main objective of the system design is to reduce the area and the power dissipation of the high voltage portion of the chip. This objective can be achieved by minimizing the complexity of the high voltage parts and transferring as many functions as possible to the low voltage back-end. This has resulted in a suitable architecture that satisfies all the short loop requirements.

This chapter starts with the general specifications of the short loops. The architecture of the high voltage front-end of a short-loop SLIC is then presented and a functional explanation of each high voltage building block is provided.

20

## 2.2 Short Loop SLIC Requirements

The requirements for short-loop SLICs differ from those of conventional ones currently employed in central offices. Traditionally, high driving voltages are used to compensate for the large voltage drops in the long loops due to their high resistances. The DC voltage of the loop is provided by a standard 48V battery located at the central office. The loop voltage can rise even higher during ringing, when an AC ring signal in the range of 90V is injected in the loop. However, the loop resistance is much smaller in short loops resulting in less stringent voltage requirements on the interface circuits. Table 2.1 presents the Bellcore recommendations on the maximum loop resistance for three different systems [1]. Due to the small loop resistance in the FITL and other short loop systems, the battery voltage can be reduced to the recommended 24V [2]. Similarly, the ring signal can be decreased to 40V or less for short loop applications.

There is no specific requirement on the loop current and therefore it is allowed to vary over a wide range. However, most low power systems limit the loop current to below 30 to 50 mA [2]. Meanwhile, the internal current of the SLIC must be kept to a minimum in order to keep the on-chip power dissipation as low as possible.

Unlike Conventional SLICs which are mainly designed for voice transmission with limited bandwidths, short loop SLICs are expected to support high speed modems and

|                                   | Max. Loop Resistance ( $\Omega$ ) |

|-----------------------------------|-----------------------------------|

| Central Office (LSSGR[3])         | 1500                              |

| Digital Loop Carrier (TR57[4])    | 900                               |

| Fiber In The Loop FITL (TR909[5]) | 17 <sup>1</sup>                   |

Table 2.1: Maximum loop resistance for different systems

1. Specified as 150 feet of no. 22 American Wire Gauge (AWG) wire at 65 C.

digital subscriber loop (DSL) systems as well. Therefore, a higher bandwidth (more than 1MHz) is expected from short loop systems.

## 2.3 Proposed Architecture for a Short-Loop SLIC

A conceptual architecture of the high voltage front-end of the short loop SLIC is illustrated in Fig. 2.1 [6-7]. A voltage-drive, current-sense approach is used in this architecture. In this configuration, the lines are driven by voltage sources while the loop current is controlled. The other alternative is to drive the loop with current sources to control the loop current. The former approach is more power efficient especially for short loops where the loop resistance is small and lower driving voltages are required. As a result, the power supply voltage of the SLIC can be reduced to decrease the overall power consumption.

The main signal path consists of a differential preamplifier and two high voltage line drivers for the Tip and Ring lines. The voice (or data) information is processed in the low voltage section of the SLIC (including codec, hybrid and control circuitry) and is provided as a low-swing (in 5V range) AC signal  $V_{in}$ . This signal is then amplified and converted to two differential signals  $V_r$  and  $V_t$  by the preamplifier stage. The preamplifier also shifts the DC levels of  $V_r$  and  $V_t$  to provide the required DC line-feed voltage. The DC level is controlled by a low voltage control signal  $V_{dc}$ , injected at the input of the preamplifier. This signal is generated by the low-voltage control circuitry based on the loop current.

Since the preamplifier is a fully-differential stage, its output common-mode voltage is independent from the input signal. Therefore, common-mode feedback circuitry is required to adjust the common-mode level of the two differential outputs of the preamplifier as illustrated in Fig. 2.1.

Fig. 2.1: Architecture of the high voltage front-end of the short-loop SLIC

The two line drivers are the most important components of the system. They must provide large currents to the loop while handling high supply voltages. Also a high bandwidth, low output impedance and high power supply rejection ratio is expected from the line driver in the presence of heavy capacitive and resistive loads. The output current of the line drivers is sensed and used in the low-voltage section of the system to perform the hybrid and loop supervision functions [8].

In a conventional SLIC, the power supply of the line drivers is usually controlled by a switching power modulator to adapt the line feed voltage according to the variable loop resistance. This method is less efficient in short loops where the loop resistance is insignificant. Instead, a simple power switch to select a high or low supply voltage can be used (in on-hook or off-hook conditions) for short-loop applications. A high supply voltage is usually used in on-hook condition when the loop has a high impedance and very small current. In off-hook mode the loop is terminated by the telephone set's impedance (600 $\Omega$

typical) and its voltage is dropped to limit the loop current. As a result, the supply voltage can be decreased by the power switch to reduce the power dissipation.

Historically, series feed resistors  $R_f$  were used in conventional SLICs to passively control the loop current as well as provide a suitable driving impedance for the loop [8]. Up to 300 $\Omega$  feed resistors are typical for conventional loops, however, smaller resistances (20 $\Omega$ to 100 $\Omega$ ) are required for short loops because of the lower line feed voltage and loop resistance.

#### 2.3.1 Preamplifier Design

The main two functions of the preamplifier are

- adjusting the DC level of the loop signals and

- converting the single-ended low voltage transmit signal to a pair of amplified differential signals.

To clarify these functions, the loop signals are conceptually illustrated in Fig. 2.2. The voice information is provided by the codec and PCM interface circuits[8] in the form of a low voltage AC signal, shown as  $V_{ac}$  in Fig. 2.2 a.  $V_{ac}$  swings within the power supply range  $V_{dd}$  (typically a 5V supply) of the low voltage portion of the system. The signals on the loop consist of a DC and an AC component, illustrated in Fig. 2.2 b. The DC component  $V_{DC}$ , is used to feed power into the loop while the AC component carries the voice information. As a result, the voltage on each line ( $V_{TIP}$  and  $V_{RING}$ ) includes a small AC signal  $V_{AC}$ , superimposed on a large DC level. Typical values are in the 1 to 2 V range for  $V_{AC}$  and 10 to 20 V for  $V_{DC}$ [9].

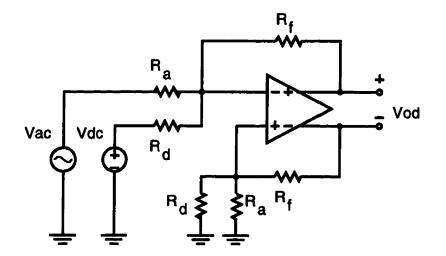

Since all signals are transmitted differentially over the loop, the AC components of  $V_{TIP}$  and  $V_{RING}$  must be 180° out of phase to inject a true differential signal into the loop. A fully-differential amplifier stage, similar to the one shown in Fig. 2.3 can be used to

Fig. 2.2: Transmitting signal levels: a) low voltage signal from Codec b) loop signal generate such signals. Using a differential opamp, the two inputs  $V_{ac}$  and  $V_{dc}$ , can be combined to generate the appropriate signal levels.

The differential output voltage  $V_{od}$  can be expressed as

$$V_{od} = \frac{R_f}{R_a} V_{ac} + \frac{R_f}{R_d} V_{dc}$$

(2.1)

where  $R_f$ ,  $R_a$  and  $R_d$  are the feedback resistors around the differential amplifier shown in Fig. 2.3. This equation implies that the gain of the amplifier for each input source can be fixed separately using  $R_a$  and  $R_d$ . Therefore, the DC level and the AC amplitude of the output voltage can be adjusted independent from each other.

In order to realize the circuit of Fig. 2.3, a high voltage differential opamp is needed. Major requirements of this opamp are minimum power dissipation and a bandwidth larger than that of the line drivers to avoid degrading the bandwidth of the whole SLIC system. A

Fig. 2.3: A differential preamplifier structure

high current driving capability is not expected from the opamp as it must only drive the input stage of the line drivers.

Equation 2.1 deals with the differential part of the output voltage. The average or common-mode component of the output voltage is independent of the input voltages and must be fixed separately. Usually, a common-mode feedback circuit is used to control the common-mode level of the output.

#### 2.3.2 Common-Mode Feedback Circuit

The common-mode output voltage of a differential amplifier may vary independently of the input signals over the whole supply voltage range, causing the output voltages to saturate at one of the supply rails. Therefore, it is necessary to control the common-mode level in a feedback loop.

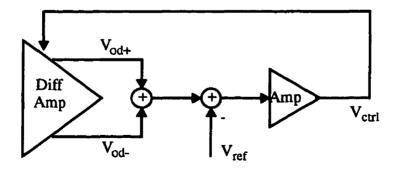

The function of the CMFB loop is illustrated in Fig. 2.4. The CMFB circuit monitors the two output voltages of the differential amplifier and adds them up to measure their

average. The result is compared with a reference level  $V_{ref}$  amplified and fed back to the differential amplifier ( $V_{ctrl}$ ) to adjust the common-mode level of its outputs. When the loop is closed, the common-mode voltage of the differential amplifier outputs is equal to the reference voltage  $V_{ref}$ .

Traditionally, two types of CMFB circuits are used in low voltage applications: switched-capacitor and continuous types [10]. The switched-capacitor CMFB circuits[11], specifically designed for switched-mode applications, are not suitable for the SLIC application. Conventional continuous CMFB circuits, either use a source-coupled voltage comparators [12] or a resistive voltage adder [13] at the input. While the first approach has a limited input range, the second one requires impractically large resistors to be able to operate with high input voltages. Therefore, none of the available designs can be used for high voltage applications. A new high voltage CMFB circuit with wide input range is required for this system. The design and implementation of this circuit is discussed in Chapter 4.

Fig. 2.4: Model of the CMFB loop

#### 2.3.3 Line Drivers

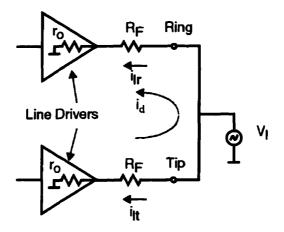

Line drivers are the most important high voltage building blocks of a SLIC system. As the actual interface to the telephone lines, they play a key role in providing large loop currents and handling high voltage signals.

Line driver specifications are mainly dictated by the requirements for the short-loop SLIC. The nominal supply voltage for short-loop SLIC is 24V [9]. In addition to the high operating voltage, a large driving current (up to 30 mA) capability is also expected from the line drivers. Meanwhile, their idle power must be kept as low as possible, preferably less than 30mW. As a result, the sum of all the internal bias currents must not exceed 1mA assuming a maximum supply voltage of 30V [9].

Another important issue in line driver design is the stability of the circuit which must be guaranteed over a wide range of load impedances. Resistive loads down to 500 $\Omega$  and capacitive loads up to 1nF may be expected at the output. In spite of such heavy loads, a unity-gain-bandwidth of more than 1MHz is required to increase the power supply rejection ratio at high frequencies and to satisfy digital subscriber line (ADSL) applications [14].

The line drivers must also have a very small output impedance. This feature is mainly required for longitudinal signal suppression [1]. Spurious noise and interference appear as longitudinal (or common-mode) signals on telephone lines. If the line driving circuits of the two lines are asymmetrical, common-mode signals can be converted to differential ones degrading the quality of transmission. This effect is characterized by longitudinal balance which is the ratio of the longitudinal to differential voltages at the output of the SLIC. This factor is a function of the matching between the driving impedances of the tip and ring terminals including the feed resistors and the output impedance of the line drivers as illustrated in Fig. 2.5. The induced noise on the twisted-pair wires is shown as a longitudinal signal source  $V_l$ .  $R_F$  is the feed resistance and  $r_o$  is the output impedance of the line driver.

Fig. 2.5: Longitudinal balance model

In the ideal case when  $R_F$  and  $r_o$  on both lines are equal, the noise currents in the ring and tip lines are the same:  $i_{lr} = i_{lt}$ , hence canceling each other. However, if there is a mismatch  $(\Delta R_F + \Delta r_o)$  between the total resistances of the tip and ring lines, then  $i_{lr} \neq i_{lt}$  and a differential current  $i_d = i_{lr} - i_{lt}$  will flow in the loop mixing with the actual voice signals. The longitudinal balance can be expressed as:

$$\frac{i_d}{i_{lr}} \cong \frac{\Delta R_F + \Delta r_o}{R_F + r_o} \tag{2.2}$$

The mismatch of the feed resistors  $\Delta R_F$ , can be controlled by choosing accurate offchip components. However, the output impedance of the line drivers may vary with operating currents, voltages and frequency. Therefore, it is not possible to maintain accurate matching for all the possible operating conditions. In order to eliminate the effect of line drivers mismatch  $\Delta r_o$ , their output impedance  $r_o$  must be less than the maximum allowable mismatch of the feed resistors  $\Delta R_F$ . For example, a longitudinal balance of 60 dB translates into a maximum allowable mismatch of 0.1% between the feed resistors. As a result, with a typical 200 $\Omega$  feed resistor, the output impedance of the line drivers must not exceed 0.2 $\Omega$ .

| Max. Supply Voltage 30V  |           |  |

|--------------------------|-----------|--|

| Max. Line Current        | 30mA      |  |

| Idle Power               | < 30mW    |  |

| Unity Gain Bandwidth     | > 1 MHz   |  |

| Output resistance (@ DC) | < 0.2Ω    |  |

| Load[15]                 | 500Ω, 1nF |  |

**Table 2.2: Major line driver specifications**

Due to lower noise and interference in a short subscriber loop, a 40 dB balance is sufficient for short loop applications [9]. However, because of lower driving voltage, the feed resistors are also smaller. With a minimum feed resistance of 20 $\Omega$ , an output resistance of less than  $0.2\Omega$  is still desirable. Finally, the line driver must occupy minimum area to be easily integrable with a large amount of low voltage circuitry required for other short loop services. The main design specifications for the line driver are summarized in Table 2.2. These specification dictate the use of an efficient circuit topology for the output stage.

#### 2.4 Summary

The specifications and characteristics of the short-loop SLIC system were discussed in this chapter. Based on the general requirements of the short-loop systems, an architecture for the high voltage front-end of the SLIC was presented. A minimum number of high voltage building blocks was used in this configuration to save both area and power. The resulting architecture is quite suitable for a single-chip implementation of a short-loop SLIC. The function and characteristics of each block were also described in this chapter. A detailed description of the implemented circuits will be presented in Chapter 4.

#### References

- [1] AM79R79 Ringing SLIC Preliminary Application Note, Advanced Micro Devices, 1996.

- [2] AM79R79 Ringing SLIC Data Sheet, Advanced Micro Devices, 1996.

- [3] Bellcore Standard, "LATA Switching Systems Generic Requirements (LSSGR): TR-NWT-000505," Issue 3, August 1995.

- [4] Bellcore Standard, "Functional Criteria for Digital Loop Carrier System: TR-NWT-000057," Issue 2, January 1993.

- [5] Bellcore Standard, "Generic Requirements and Objectives for Fiber In The Loop Systems: TR-NWT-000909," Issue 2, December 1993.

- [6] M. Aliahmad, C.A.T. Salama, "A Short Loop SLIC in a Submicron BiCMOS Technology," Proceedings of the Ninth International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 329-332, 1997

- [7] M. Aliahmad, C.A.T. Salama, "Integration of a Short Loop SLIC in a Low Voltage Submicron BiCMOS Technology," Accepted for publication in *IEEE J. Solid-State Circuits*, 1997.

- [8] W. D. Reeve, Subscriber Loop Signaling and Transmission Handbook, Analog, IEEE Press, New York, 1992.

- [9] Nortel staff, Private Communications, 1995.

- [10] J. F. Duque-Carillo, "Control of the Common-Mode Component in CMOS Continuous Time Fully Differential Signal Processing," Analog Integrated Circuits and Signal Processing Journal, vol. 4, pp. 131-140, 1993.

- [11] R. Castello, and P. R. Gray, "A High-Performance Micropower Switched-Capacitor Filter," IEEE J. Solid-State Circuits, vol. 20, pp. 1122-1132, 1985.

- [12] M. Banu, J. M. Khoury, and Y. Tsividis, "Fully Differential Operational Amplifiers with Accurate Output Balancing," *IEEE J. Solid-State Circuits*, vol. 23, pp. 1410-1414, 1988.

- [13] J. Babanezhad, "A Rail-to-Rail CMOS OpAmp," IEEE J. Solid-State Circuits, vol. 23, pp. 1414-1417, 1988.

- [14] W. D. Reeve, Subscriber Loop Signalling and Transmission Handbook, Digital, IEEE Press, New York, 1995.

- [15] R. Castello, F. Lari, M. Siligoni, and L. Tomasini, "100-V High-performance amplifiers in BCD technology for SLIC applications," *IEEE J. Solid-State Circuits*, vol. 27, pp. 1255-1263, 1992.

# **CHAPTER 3**

# **BiCMOS Compatible High Voltage Device Design**

#### **3.1 Introduction**

The choice of a suitable technology is the key issue in the integration of a short-loop SLIC. Traditionally, high voltage bipolar processes were used to implement central office SLIC circuits[1-2]. Recent advances in power MOS devices has led to the development of BCD technologies which can implement Bipolar, CMOS and DMOS devices on the same chip [3-6]. However, being specifically designed for high voltage applications, such processes generally involve more complexity, less density and much higher costs as compared to VLSI CMOS or BiCMOS processes.

As mentioned in Chapter 1, the implementation of short-loop SLICs in future local access systems will require a high level of integration at minimum cost. Since the high voltage blocks only comprise a small part of the system (which includes a significant amount of high-performance, high-speed, low voltage circuitry), an advanced low voltage VLSI process with enhanced high voltage capabilities is more suitable for this application than a dedicated high voltage IC technology.

This thesis is the first attempt at implementing a short-loop SLIC using a submicron low voltage BiCMOS process. The high voltage capabilities of this process are provided by lateral extended-drain NMOS and PMOS transistors [7-9]. In this chapter, after a brief review of the two versions of the BiCMOS process (i.e. BATMOS-5 and BATMOS-10), the structure and characteristics of the high voltage devices, implemented in this process, are discussed. Fabricated devices are characterized and a set of SPICE models are developed to facilitate the design of high voltage circuits.

#### **3.2 BATMOS-5 Process**

The BATMOS process used to implement the high voltage circuits in this thesis is a  $0.8\mu$ m BiCMOS process available through Nortel [10]. The original BATMOS-5 is a 5 V process. By adding a few more masks and processing steps, another version of the process called BATMOS-10 was developed at Nortel [11]. This version of process was designed to provide 10V NMOS devices as well as PNP bipolar transistors. The features of BATMOS-10 process will be discussed in the next section.

The submicron CMOS devices in the BATMOS process are very attractive for highdensity, low-power logic and control circuits, while the bipolar transistors are more suitable for high-gain, high-speed analog stages because of their high transconductance. In addition, the bipolar devices offer the best performance in high precision linear blocks such as current mirrors as a result of their superior matching.

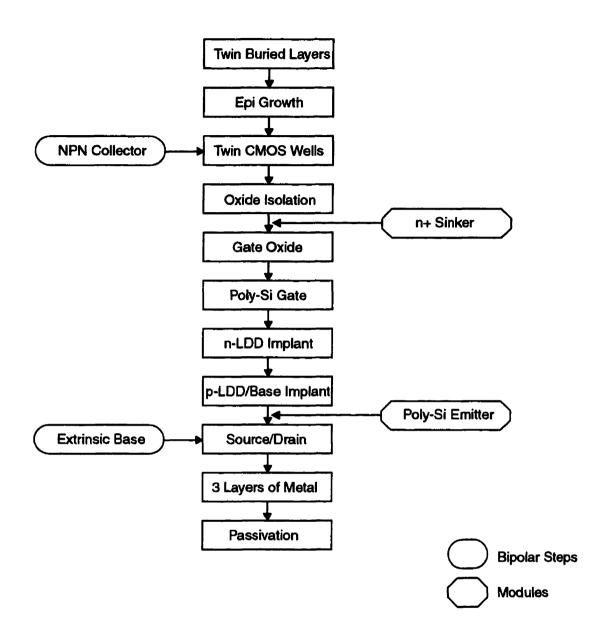

Fig. 3.1 illustrates the flow of the BATMOS-5 process [13]. Starting with a p-type substrate, the thin buried layers are defined followed by the growth of a very lightly doped 1.3 $\mu$ m epi-layer. The buried layers are used to reduce the collector resistance of the bipolar devices as well as improve the latch-up immunity of CMOS circuits. Self-aligned n and p wells are formed next following by the growth of a thick field oxide for isolation. A n+ sinker implantation is performed at this stage to reduce the collector resistance of the bipolar transistors.

In the next step, a 175Å gate oxide is grown and a blanket threshold voltage adjustment implantation is carried out afterwards. The poly-silicon gates and poly-poly capacitors are

Fig. 3.1: BATMOS-5 process flow

then formed followed by the low doped drain (LDD) implantations. The LDD regions are used in the CMOS devices to suppress the hot carrier effects. The poly-silicon emitter of the bipolar devices is created in the next step. The source and drain regions of CMOS components are formed along with the extrinsic base of the bipolar devices. The process is completed with three levels of metallization and passivation.

Fig. 3.2: Cross section of the BiCMOS process [10]

A cross section of the BATMOS-5 process is illustrated in Fig. 3.2. The thin epi-layer is used to obtain a high speed vertical NPN transistor. However, it severely limits the ability to implement high voltage structures in this process. The breakdown voltage of the CMOS devices is limited to 7V and that of the bipolar transistors to 8V. The bipolar transistors have a peak cutoff frequency of 12 GHz with a minimum emitter area of  $0.8x4 \,\mu m^2$ . The  $0.8\mu m$  CMOS components have good immunity to hot carrier injection effects and latch-up through the use of low-doped drain (LDD) structures and buried layers respectively.

This process also provides poly-silicon resistors with sheet resistances of 30 and 750  $\Omega$ /sq and high power 120 $\Omega$ /sq diffusion resistors useful for high current densities. The high quality poly-poly capacitors offer a large capacitance per unit area (1.15 fF/ $\mu$ m<sup>2</sup>). However, the voltage across them must not exceed the 5 V limit. Therefore they cannot be used in high voltage applications. Table 3.1 summarizes the available devices in this process.

| Device    | Parameter         |                         |

|-----------|-------------------|-------------------------|

| CMOS      | L <sub>eff</sub>  | 0.66 µm                 |

|           | V <sub>t</sub>    | 0.8 V                   |

|           | BV                | 7 V                     |

| Bipolar   | Emitter Area      | 4x0.8 μ <sup>2</sup>    |

|           | f <sub>t</sub>    | 12 GHz                  |

|           | BV <sub>ceo</sub> | 8 V                     |

| Capacitor | C <sub>p-p</sub>  | 1.15 fF/μm <sup>2</sup> |

|           | BV                | 5 V                     |

| Resistors | Rpoly             | 750 Ω/sq                |

|           | LRpoly            | 30 Ω/sq                 |

|           | Rdiff             | 120 Ω/sq                |

Table 3.1: Available devices in the 0.8µm BiCMOS

## 3.3 BATMOS-10 Process

Modularity is one of the key features of the BATMOS process which allows the selection of optional modules without any impact on the remainder of the process. The BATMOS-10 version is a result of adding such modules to the original BATMOS-5 process. The extra modules have been developed by Nortel [11] with design support from the University of Toronto to provide two additional layers namely n-subwell and high voltage (HV) n-well.

The useful feature of BATMOS-10 process is the implementation of a n-subwell layer. The n-subwell is an extra n-type layer, located underneath the buried layers. This is implemented by using an additional mask and a diffusion step at the very beginning of the process (i.e., before the definition of the buried layers) as shown in Fig. 3.3. Therefore, it

Fig. 3.3: NSUBWELL processing step

has no effect on the buried layers or well regions leaving the performance of the low voltage components intact.

The main use of the n-subwell is to isolate the p-well region from the p-substrate. This allows the body of the NMOS devices to be disconnected from ground, eliminating the body effect in high-side configurations. An isolated p-well can also be used as the collector of a vertical PNP transistor. In fact, using additional n-base and p-emitter processing modules, a high quality vertical PNP device has been developed at Nortel with its cross section illustrated in Fig. 3.4. The availability of complementary bipolar devices offers great advantages in designing analog circuits with this process.

Fig. 3.4: Structure of PNP transistor in the 10V BiCMOS process

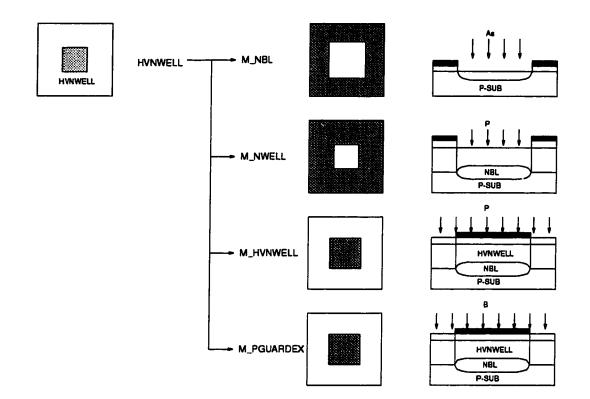

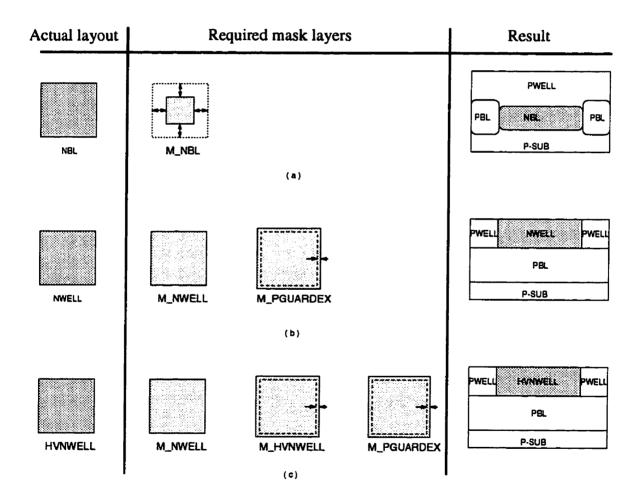

The HV n-well is similar to the n-well with a much lower doping concentration. It has been designed for implementing NMOS devices with a breakdown voltage of 10 V. While the HV n-well must be implemented together with the n-well, it must not affect the characteristics of other layers including the n-well itself. Therefore, an extra mask (M\_HVNWELL) and ion-implantation step is used with a much lower implant dose as shown in Fig. 3.5.