### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality  $6^{\circ} \times 9^{\circ}$  black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

# NOTE TO USERS

Page(s) not included in the original manuscript are unavailable from the author or university. The manuscript was microfilmed as received.

97

This reproduction is the best copy available.

UMI

McGill University Department of Electrical Engineering Montréal, Québec, Canada

## Compression and Decompression of Test Data for Scan Based Designs

Nadime Zacharia

B.Eng. (McGill) 1994

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfilment of the requirements for the degree of

Master of Engineering

December 1996

© Nadime Zacharia, 1996

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre rélérence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-44048-6

## Abstract

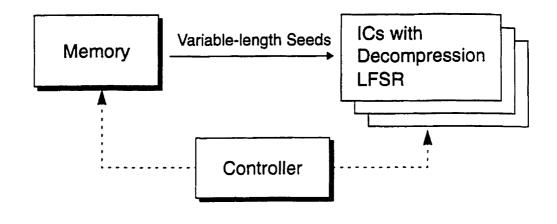

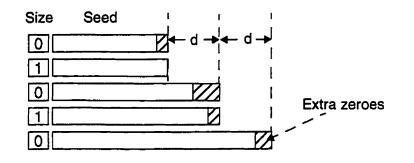

Traditional methods to test integrated circuits (ICs) require enormous amount of memory, which make them increasingly expensive and unattractive. This thesis addresses this issue for scan-based designs by proposing a method to compress and decompress input test patterns. By storing the test patterns in a compressed format, the amount of memory required to test ICs can be reduced to manageable levels. The thesis describes the compression and decompression scheme in details. The proposed method relies on the insertion of a decompression unit on the chip. During test application, the patterns are decompressed by the decompression unit as they are applied. Hence, decompression is done on-the-fly in hardware and does not slow down test application.

The design of the decompression unit is treated in depth and a design is proposed that minimizes the amount of extra hardware required. In fact, the design of the decompression unit uses flip-flops already on the chip: it is implemented without inserting any additional flip-flops.

The proposed scheme is applied in two different contexts: (1) in (external) deterministicstored testing, to reduce the memory requirements imposed on the test equipment; and (2) in built-in self test, to design a test pattern generator capable of generating deterministic patterns with modest area and memory requirements.

Experimental results are provided for the largest ISCAS'89 benchmarks. All of these results point to show that the proposed technique greatly reduces the amount of test data while requiring little area overhead. Compression factors of more than 20 are reported for some circuits.

Compression and Decompression of Test Data for Scan Based Designs

Résumé

Les méthodes de génération de vecteurs de test pré-déterminés requièrent des quantités impressionnantes de mémoire, ce qui les rendent de plus en plus impopulaires. Cette thèse propose une nouvelle méthode de génération de vecteurs pré-déterminés et vise tout particulièrement les circuits numériques avec une ou plusieurs chaînes de balayage. La technique compresse les vecteurs avant de les stocker, ce qui minimise la quantité de mémoire requise. Ils sont, par la suite, générés à l'aide d'une unité de décompression incorporée sur la puce.

La technique utilisée pour compresser et décompresser les vecteurs de test est décrite en détailles, de même que toute la théorie de base nécessaire à sa réalisation. De plus, la conception de l'unité de décompression est traitée en profondeur. Il est démontré que cette unité peut être réalisée avec quelques portes logiques, sans nécessiter aucune bascule.

La méthode proposée dans cette thèse peut être appliquée dans deux cas différents: (1) pour réduire de façon significative la quantité de mémoire qui doit être stockée par les équipements de test; et (2) pour la conception d'une unité de génération de vecteurs de test autonome qui peut émettre des vecteurs pré-déterminés sans nécessiter des quantités énormes de mémoire et de silicone. Cette dernière application est particulièrement importante pour les circuits avec fonction de vérification autonome et intégrée.

De nombreuses expérience ont été faite avec les circuits ISCAS89. Les résultats tendent à démontrer que la nouvelle méthode proposée dans cette thèse peut émettre des vecteurs pré-déterminés sans infliger des quantités excessives de données, et sans utiliser trop de silicone.

I would like to acknowledge Dr. Rajski and Dr. Tyszer for their guidance throughout the course of my studies. Their vision, hard work and their enthusiasm greatly contributed to this work. I will benefit from their advice, and their teaching for the rest of my career.

During my stay in the MACS laboratory, I deeply appreciated the friendship of the student members and staff. I would like to say hello to Mark Kassab, Nagesh Tamarapalli, Nilanjan Mukherjee, Victor Zia, Kasia Radecka, Vincent Leung, Jacek Slaboszawicz, and Alain Magloire, to name a few. They all added to my stay in the MACS laboratory. I wish them luck and happiness.

The experiments in the thesis were possible thanks to the help of many people. I am grateful to Robert C. Aitken and Pieter Trouborst for providing samples of test data for some industrial circuits. I also would like to thank John. A. Waicukauski for adapting his test generation programs to the methods proposed in the thesis.

On a more personal level, I would like to thank my parents, Abdallah and Helene, and my girlfriend Martine, for their encouragement and love all throughout my studies. I also would like to thank my brother Karim and my sister Nadia.

This work would not have been possible without monetary support. I was very privileged to receive several awards and bursaries throughout my studies. In particular, I acknowledge receiving two summer research bursaries from NSERC and the NSERC award (master level).

# Table of Contents

| RésuméivAcknowledgementsvTable of ContentsviList of FiguresxList of TablesxiChapter 1Introduction1.1Overview of Thesis6Chapter 2Basics of Logic Testing82.1Introduction82.1.12.1.2Testing92.1.22.15Single Stuck-at and Other Fault Models112.2.12.2.2Testing for Faults132.32.4Test Pattern Generation172.4.12.4.1Exhaustive172.4.22.4.3Pseudo-random182.4.32.4.3Pseudo-random                                                                                                                                                                                                                                                                                                                                                                                             | Abstrac   | it i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ii                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Table of ContentsviList of FiguresxList of TablesxiChapter 1Introduction1.1Overview of Thesis6Chapter 2Basics of Logic Testing82.1Introduction82.1.12.1.2Testing92.22.12Testing and Tests112.2.12.2.1Single Stuck-at and Other Fault Models2.3Test Generation and Fault Simulation142.42.4Test Pattern Generation172.4.12.4.2Deterministic18                                                                                                                                                                                                                                                                                                                                                                                                                               | Résumé    | i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | v                               |

| List of Figures       x         List of Tables       xi         Chapter 1       Introduction       1         1.1       Overview of Thesis       6         Chapter 2       Basics of Logic Testing       8         2.1       Introduction       8         2.1.1       Huffman Model of Sequential Circuits       9         2.1.2       Testing       9         2.1.2       Testing       11         2.2.1       Single Stuck-at and Other Fault Models       12         2.2.2       Testing for Faults       13         2.3       Test Generation and Fault Simulation       14         2.4       Test Pattern Generation       17         2.4.1       Exhaustive       17         2.4.2       Deterministic       18                                                       | Acknow    | vledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | v                               |

| List of Tables       xi         Chapter 1       Introduction       1         1.1       Overview of Thesis       6         Chapter 2       Basics of Logic Testing       8         2.1       Introduction       8         2.1       Introduction       9         2.1.1       Huffman Model of Sequential Circuits       9         2.1.2       Testing       9         2.1.2       Testing       9         2.1.2       Testing for Faults       11         2.2.1       Single Stuck-at and Other Fault Models       12         2.2.2       Testing for Faults       13         2.3       Test Generation and Fault Simulation       14         2.4       Test Pattern Generation       17         2.4.1       Exhaustive       17         2.4.2       Deterministic       18 | Table of  | f Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | /i                              |

| Chapter 1       Introduction       1         1.1       Overview of Thesis       6         Chapter 2       Basics of Logic Testing       8         2.1       Introduction       8         2.1.1       Huffman Model of Sequential Circuits       9         2.1.2       Testing       9         2.1.2       Testing       9         2.1.2       Testing       11         2.2.1       Single Stuck-at and Other Fault Models       12         2.2.2       Testing for Faults       13         2.3       Test Generation and Fault Simulation       14         2.4       Test Pattern Generation       17         2.4.1       Exhaustive       17         2.4.2       Deterministic       18                                                                                   | List of F | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | x                               |

| 1.1       Overview of Thesis       6         Chapter 2       Basics of Logic Testing       8         2.1       Introduction       8         2.1.1       Huffman Model of Sequential Circuits       9         2.1.2       Testing       9         2.1       Testing       9         2.1       Single Stuck-at and Other Fault Models       12         2.2.2       Testing for Faults       13         2.3       Test Generation and Fault Simulation       14         2.4       Test Pattern Generation       17         2.4.1       Exhaustive       17         2.4.2       Deterministic       18                                                                                                                                                                         | List of I | fables »                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ci                              |

| Chapter 2Basics of Logic Testing82.1Introduction82.1.1Huffman Model of Sequential Circuits92.1.2Testing92.1.2Testing92.2Fault Models and Tests112.2.1Single Stuck-at and Other Fault Models122.2.2Testing for Faults132.3Test Generation and Fault Simulation142.4Test Pattern Generation172.4.1Exhaustive172.4.2Deterministic18                                                                                                                                                                                                                                                                                                                                                                                                                                           | Chapter   | r 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                               |

| 2.1       Introduction       8         2.1.1       Huffman Model of Sequential Circuits       9         2.1.2       Testing       11         2.2.1       Single Stuck-at and Other Fault Models       12         2.2.2       Testing for Faults       13         2.3       Test Generation and Fault Simulation       14         2.4       Test Pattern Generation       17         2.4.1       Exhaustive       17         2.4.2       Deterministic       18                                                                                     | 1.1       | Overview of Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                               |

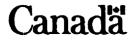

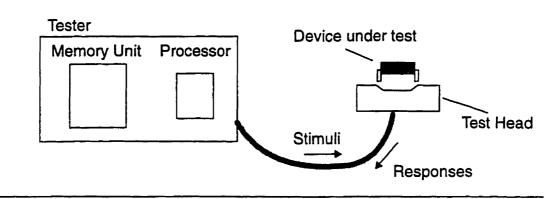

| 2.1.1Huffman Model of Sequential Circuits92.1.2Testing92.2Fault Models and Tests112.2.1Single Stuck-at and Other Fault Models122.2.2Testing for Faults132.3Test Generation and Fault Simulation142.4Test Pattern Generation172.4.1Exhaustive172.4.2Deterministic18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Chapter   | r 2 Basics of Logic Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8                               |

| 2.1.2 Testing92.2 Fault Models and Tests112.2.1 Single Stuck-at and Other Fault Models122.2.2 Testing for Faults132.3 Test Generation and Fault Simulation142.4 Test Pattern Generation172.4.1 Exhaustive172.4.2 Deterministic18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.1       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                               |

| 2.2       Fault Models and Tests       11         2.2.1       Single Stuck-at and Other Fault Models       12         2.2.2       Testing for Faults       13         2.3       Test Generation and Fault Simulation       14         2.4       Test Pattern Generation       17         2.4.1       Exhaustive       17         2.4.2       Deterministic       18                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |

| 2.2.1Single Stuck-at and Other Fault Models122.2.2Testing for Faults132.3Test Generation and Fault Simulation142.4Test Pattern Generation172.4.1Exhaustive172.4.2Deterministic18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           | 2.1.1 Huffman Model of Sequential Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9                               |

| 2.2.2 Testing for Faults132.3 Test Generation and Fault Simulation142.4 Test Pattern Generation172.4.1 Exhaustive172.4.2 Deterministic18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |

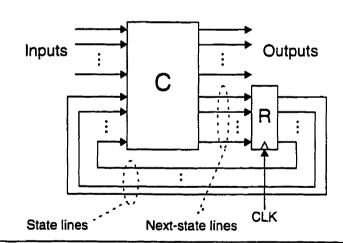

| 2.3 Test Generation and Fault Simulation       14         2.4 Test Pattern Generation       17         2.4.1 Exhaustive       17         2.4.2 Deterministic       18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.2       | 2.1.2 Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                               |

| 2.4 Test Pattern Generation       17         2.4.1 Exhaustive       17         2.4.2 Deterministic       18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.2       | 2.1.2 Testing<br>Fault Models and Tests 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9<br>1                          |

| 2.4.1       Exhaustive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.2       | <ul> <li>2.1.2 Testing</li> <li>Fault Models and Tests</li> <li>2.2.1 Single Stuck-at and Other Fault Models</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9<br>1<br>2                     |

| 2.4.2 Deterministic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | 2.1.2 Testing          Fault Models and Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9<br>1<br>2<br>3                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.3       | 2.1.2 Testing       Image: Stuck and Tests         Fault Models and Tests       Image: Stuck and Other Fault Models         2.2.1 Single Stuck at and Other Fault Models       Image: Stuck and Image: Stu | 9<br>1<br>2<br>3<br>4           |

| 2.4.3 Pseudo-random                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.3       | 2.1.2 Testing       Image: Stuck and Tests         Fault Models and Tests       1         2.2.1 Single Stuck-at and Other Fault Models       1         2.2.2 Testing for Faults       1         Test Generation and Fault Simulation       1         Test Pattern Generation       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9<br>1<br>2<br>3<br>4<br>7      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.3       | 2.1.2 Testing       Image: Stuck and Tests         Fault Models and Tests       1         2.2.1 Single Stuck-at and Other Fault Models       1         2.2.2 Testing for Faults       1         Test Generation and Fault Simulation       1         Test Pattern Generation       1         2.4.1 Exhaustive       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9<br>1<br>2<br>3<br>4<br>7<br>7 |

|         | 2.4.4   | Mixed-mode (Hybrid)                             | 19       |

|---------|---------|-------------------------------------------------|----------|

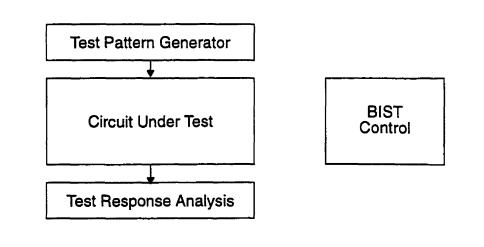

| 2.5     | Test R  | esponse Analysis                                | 20       |

| 2.6     | Desigr  | n for Testability                               |          |

|         | 2.6.1   | Ad Hoc                                          | 22       |

|         | 2.6.2   | Structured (Scan and Built-In Self Test)        | 23       |

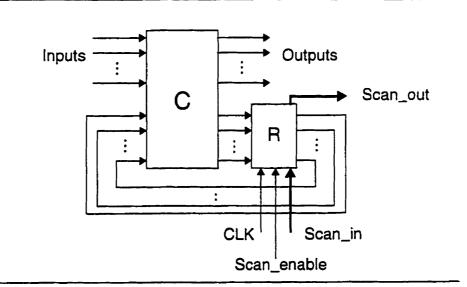

| Chapter | -3 S    | can Design Methodology                          | 26       |

| 3.1     | Introd  | uction                                          | 26       |

| 3.2     | Full So | can Designs                                     | 26       |

|         | 3.2.1   | Modes of Operations                             | 27       |

|         | 3.2.2   | Test Pattern                                    | 28       |

|         | 3.2.3   | Test Generation                                 | 28       |

|         | 3.2.4   | Trade-offs of Scan Designs                      | 29       |

| 3.3     | Multip  | ble Scan Chains                                 | 30       |

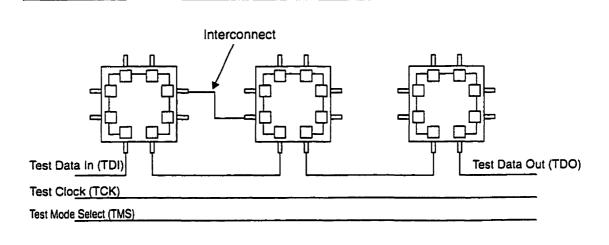

| 3.4     | Bound   | lary Scan                                       |          |

| 3.5     | Test P  | attern Generation for Scan                      |          |

|         | 3.5.1   | Classical Approaches                            | 32       |

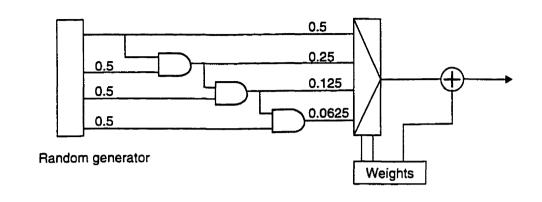

|         | 3.5.2   | Weighted Random Pattern Testing                 | 33       |

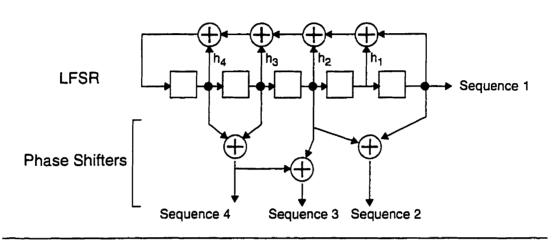

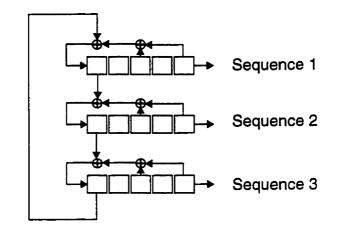

|         | 3.5.3   | Reseeding of Multiple-Polynomial Shift Register | 35       |

| 3.6     | Scan a  | and Built-In Self Test                          | 38       |

|         | 3.6.1   | Test Pattern Generators for BIST                | 38       |

| 3.7     | Motiv   | ation of Thesis                                 |          |

| Chapter | ·4 E    | Encoding Test Cubes as Variable-Length Seeds of | a Linear |

|         | F       | Feedback Shift Register                         | 44       |

| 4.1     | Introd  | uction                                          | 44       |

| 42      | Basic   | Theory of LFSRs                                 | 45       |

| •••     |         |                                                 |          |

|                   | 4.2.2                                                                                   | Characteristic Polynomial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47                                                        |

|-------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

|                   | 4.2.3                                                                                   | Relation between Seed and Generated Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 48                                                        |

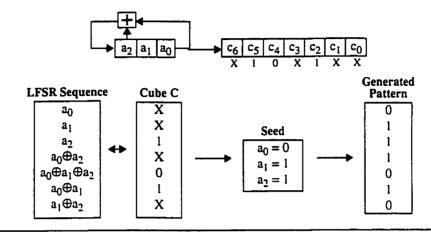

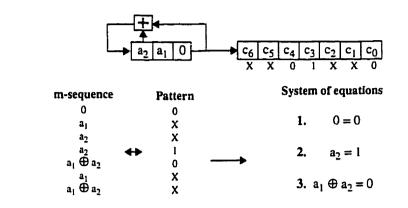

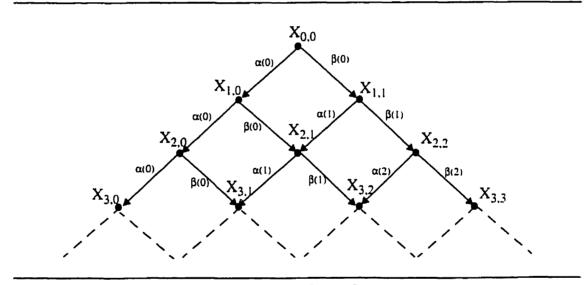

| 4.3               | LFSR                                                                                    | -Coded Cubes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50                                                        |

|                   | 4.3.1                                                                                   | Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51                                                        |

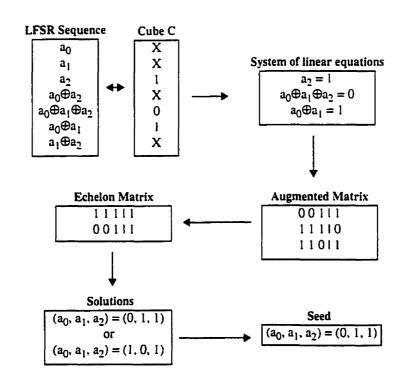

|                   | 4.3.2                                                                                   | Solving System of Linear Equations (modulo 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 52                                                        |